## **SERVICE MANUAL FOR**

<u>8175</u>

BY: Jacey Liu

### TESTING TECHNOLOGY DEPARTMENT / TSSC

Apr. 2002

# CONTENTS

| 1. Hardware Engineering Specification                   | 4   |

|---------------------------------------------------------|-----|

| 1.1 Introduction                                        | 4   |

| 1.2 System Architecture                                 | 5   |

| 1.3 Electrical Characteristic                           | 22  |

| 1.4 APPENDIX                                            |     |

| 1.5 BIOS Specification                                  | 39  |

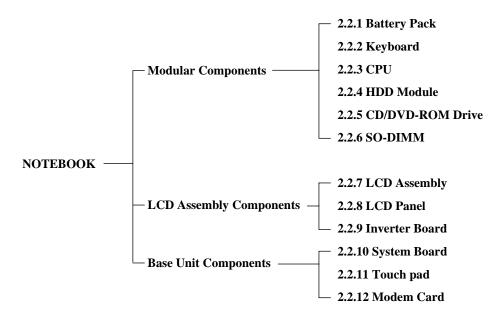

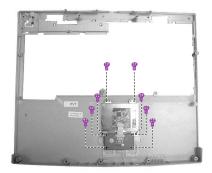

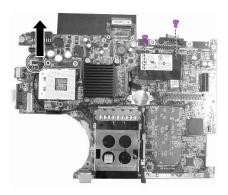

| 2. System Assembly & Disassembly                        | 81  |

| 2.1 System View                                         | 81  |

| 2.2 System Disassembly                                  | 85  |

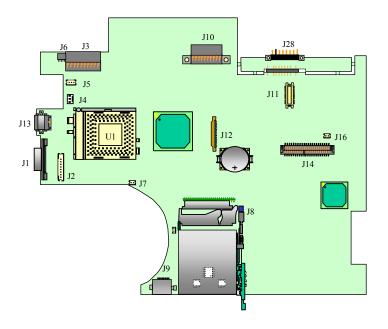

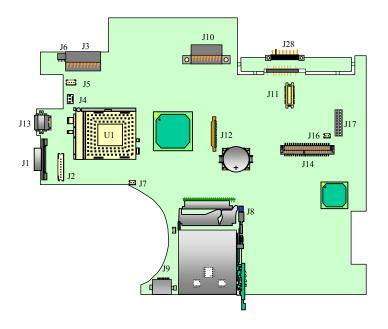

| 3. Definition & Location Connectors / Switches Setting  | 103 |

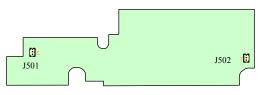

| 3.1 Main Board                                          | 103 |

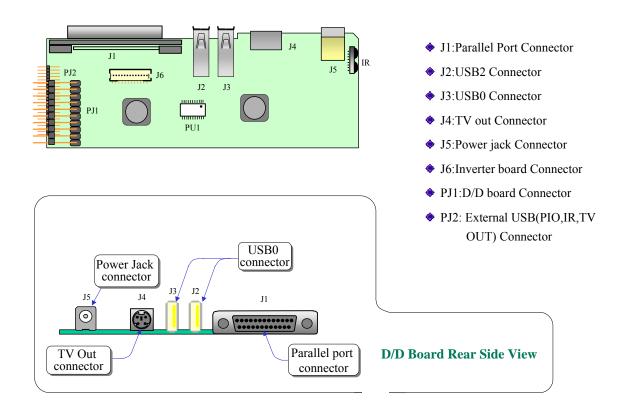

| 3.2 D/D Board                                           | 106 |

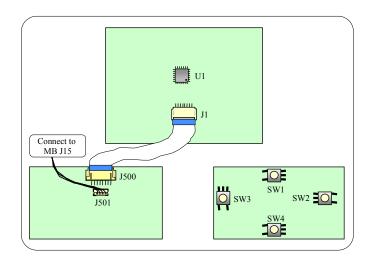

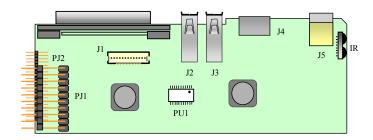

| 3.3 Touch PAD Board                                     | 107 |

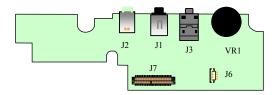

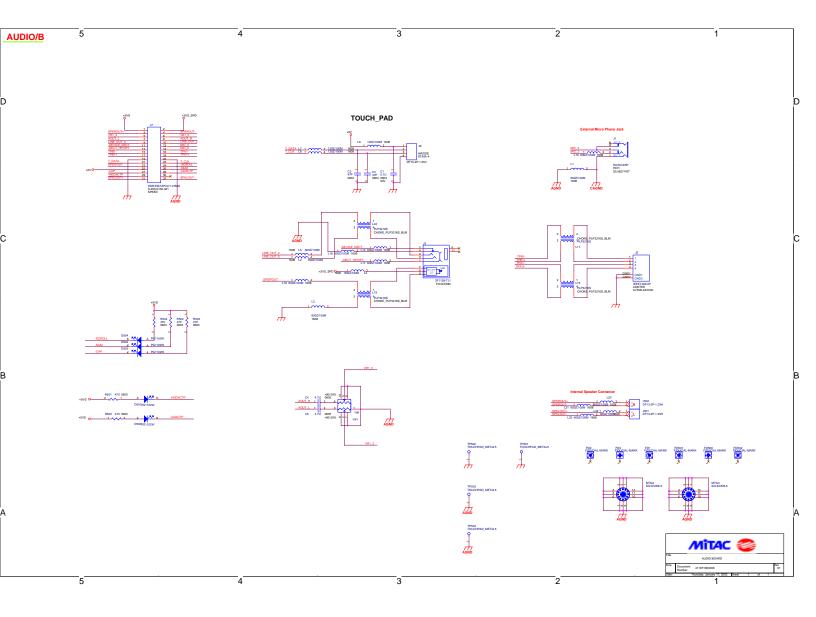

| 3.4 Audio Board                                         | 108 |

| 4. Definition & Location Major Components               | 109 |

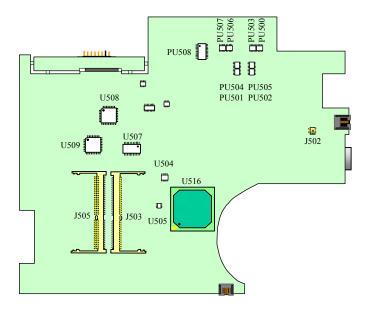

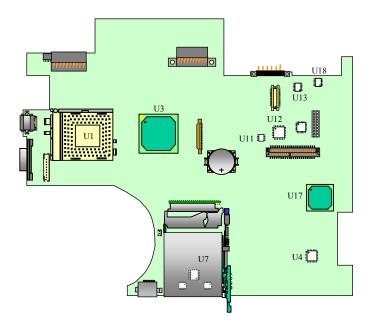

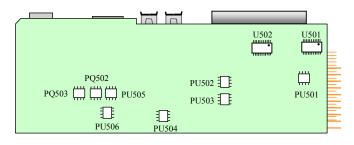

| 4.1 Main Board                                          | 109 |

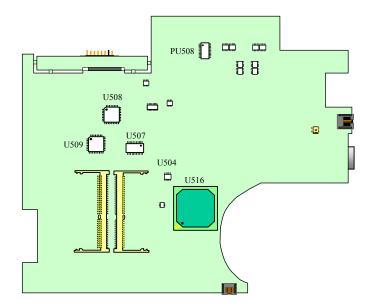

| 4.2 D/D Board                                           | 111 |

| 5. Pin Descriptions of Major Components                 | 112 |

| 5.1 Pentium 4(Willamette/Northwood) Micro-FCPGA 478 pin | 112 |

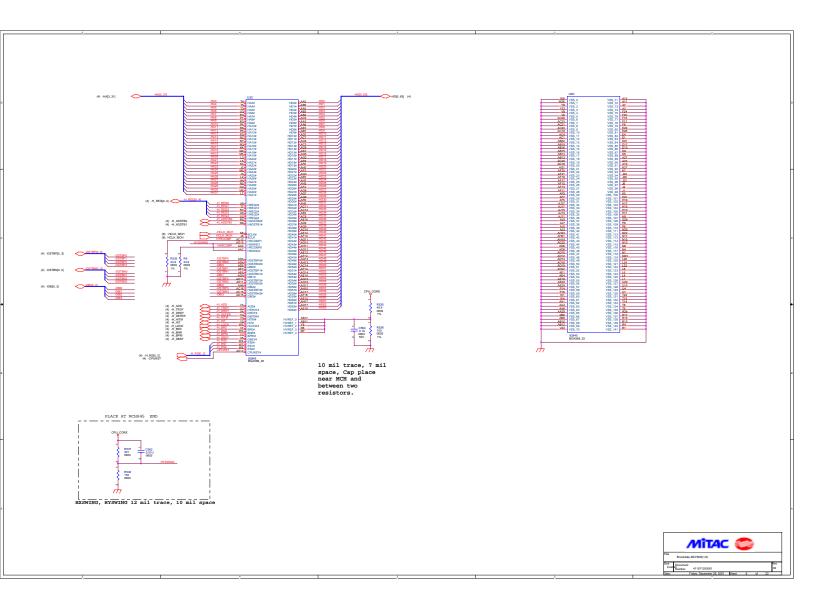

| 5.2 Intel 82845(Brookdale Memory Controller HUB)        | 118 |

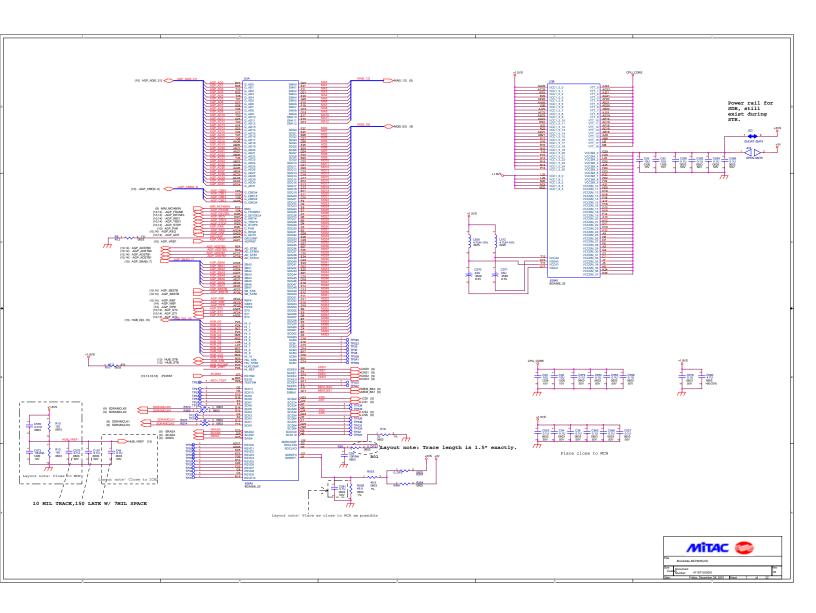

| 5.3 Intel 82801BA(I/O Controller HUB )                  | 125 |

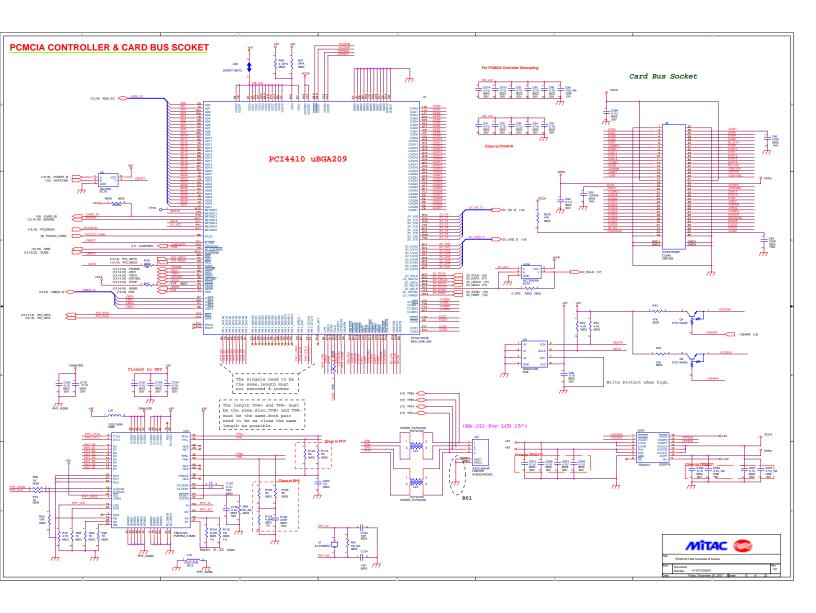

| 5.4 PCI4410(PCMCIA/1394 LINK Controller )               | 130 |

$Downloaded \ from \ \underline{www.Manualslib.com} \ \ manuals \ search \ engine$

### **CONTENTS**

| 6. System Block Diagram 136                            | j |

|--------------------------------------------------------|---|

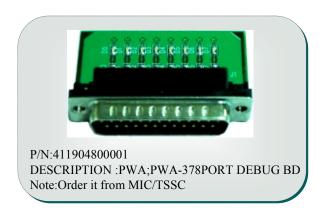

| 7. Maintenance Diagnostic                              | , |

| 7.1 Introduction 138                                   | 3 |

| 7.2 Error Codes                                        | 3 |

| 7.3 Debug Card                                         | ) |

| 8. Trouble Shooting                                    | 2 |

| 8.1 No Power                                           | 3 |

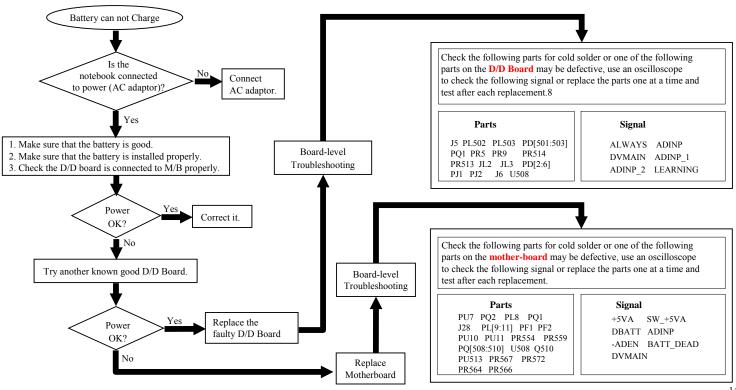

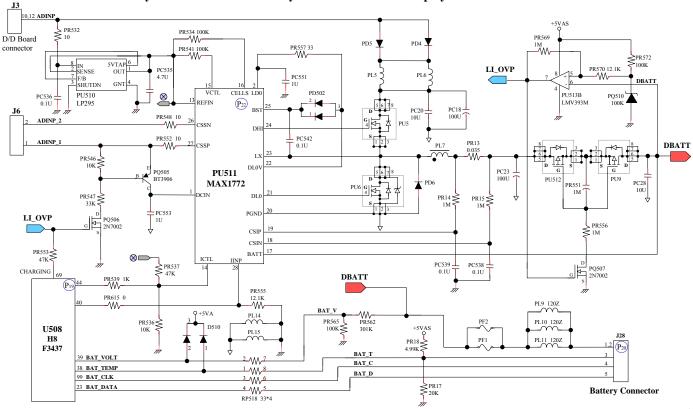

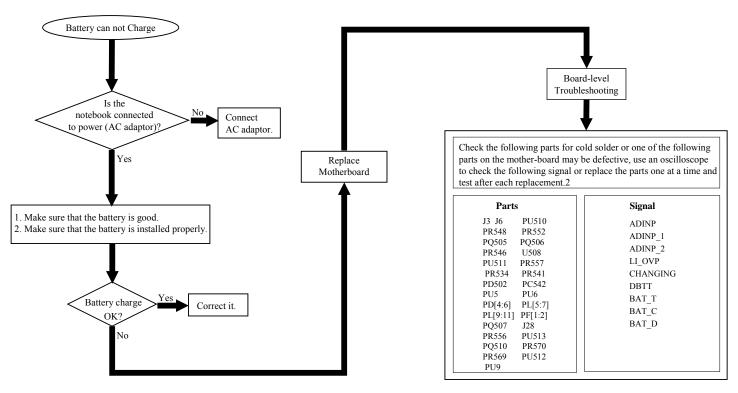

| 8.2 Battery Can not Be Charged                         | 3 |

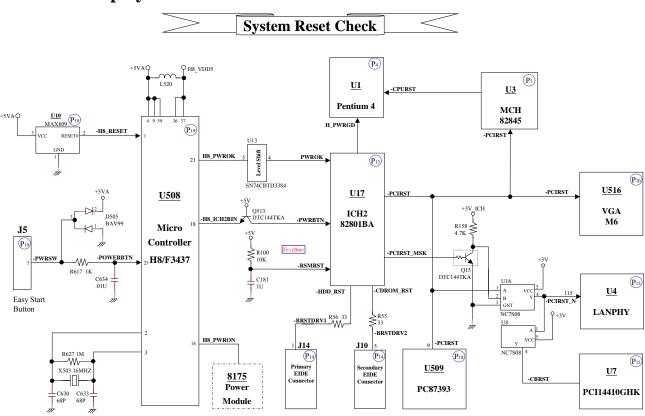

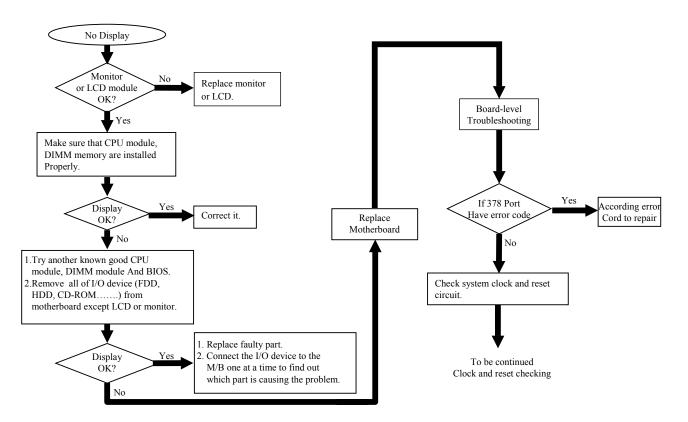

| 8.3 No Display                                         | l |

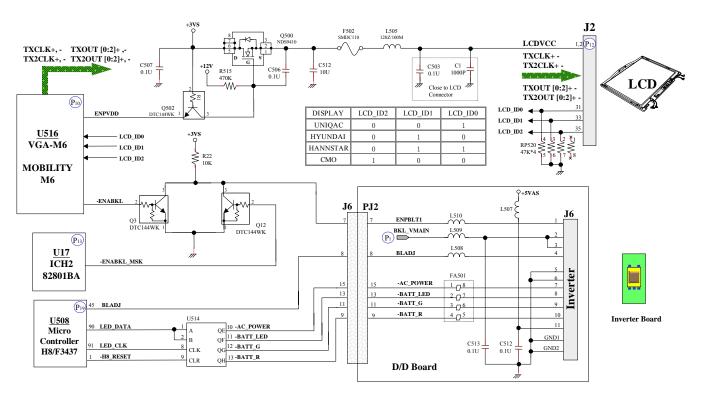

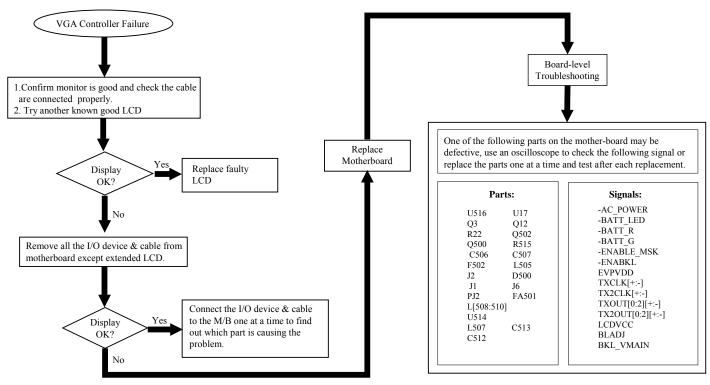

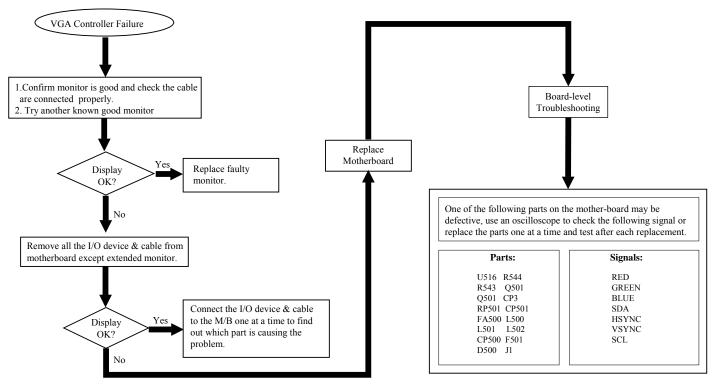

| 8.4 VGA Controller Failure LCD No Display              | 3 |

| 8.5 VGA Controller Failure External Monitor No Display | 5 |

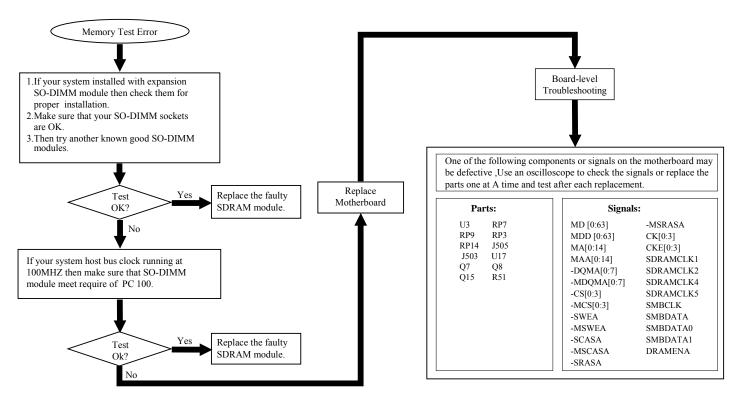

| 8.6 Memory Test Error                                  | 1 |

| 8.7 Keyboard(K/B) and Touch Pad(T/B) Test Error        |   |

| 8.8 Hard Drive Test Error                              |   |

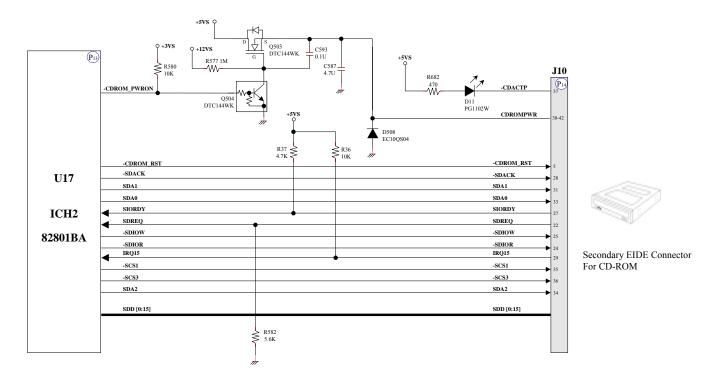

| 8.9 CD-ROM Drive Test Error                            | 3 |

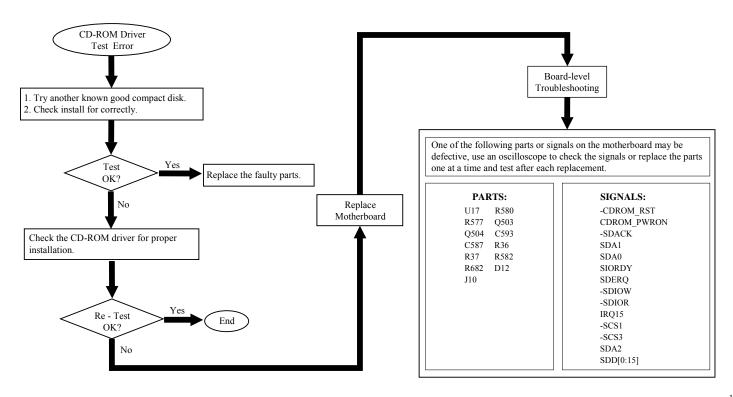

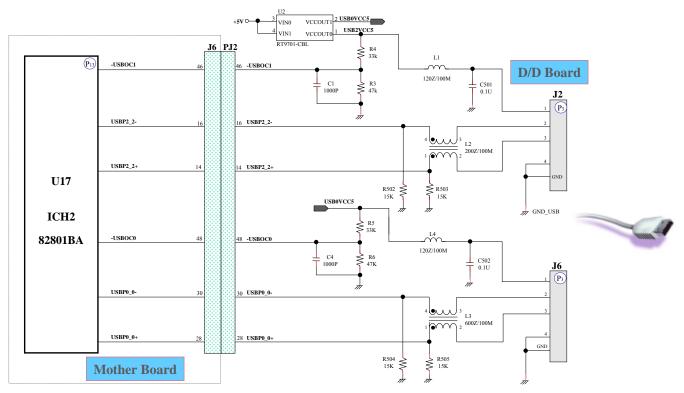

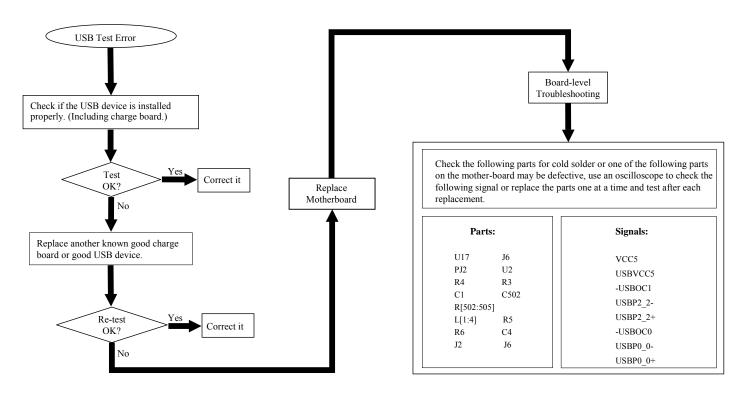

| 8.10 USB Port Test Error                               | j |

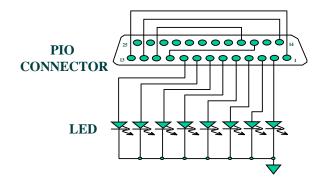

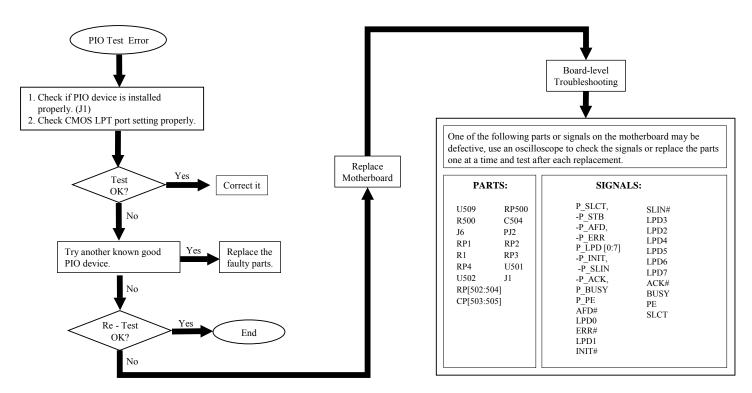

| 8.11 PIO Port Test Error                               | 7 |

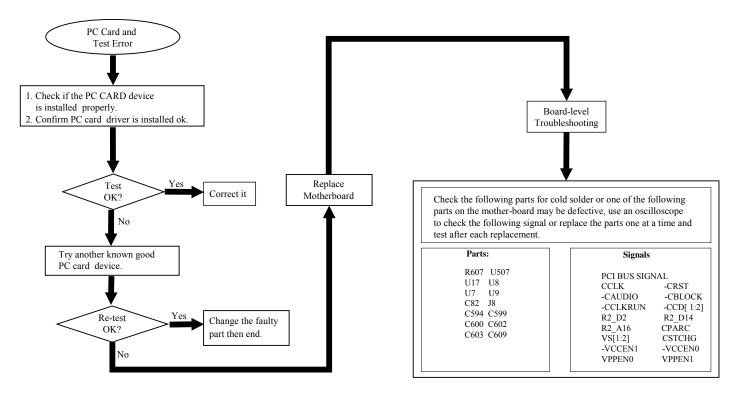

| 8.12 PC-Card Failure                                   | ) |

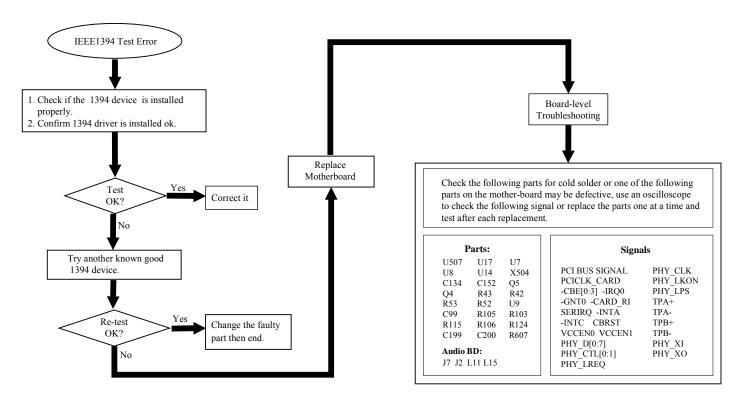

| 8.13 IEEE1394 Failure                                  |   |

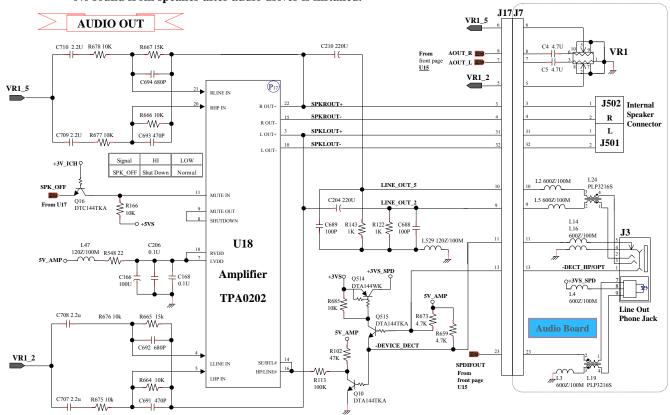

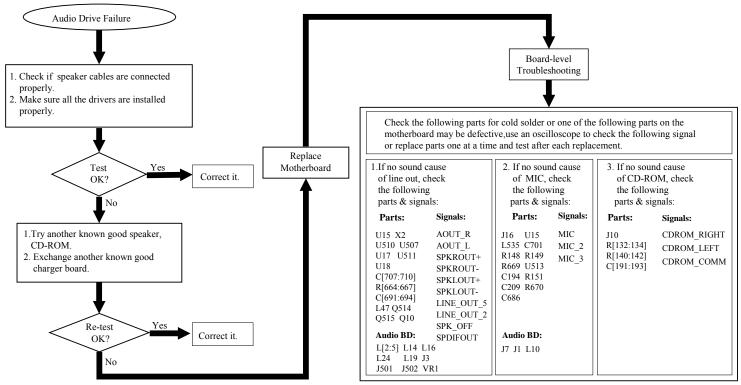

| 8.14 Audio Failure                                     | - |

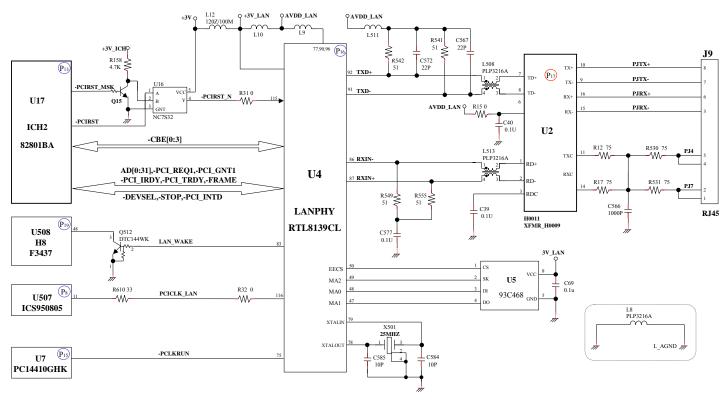

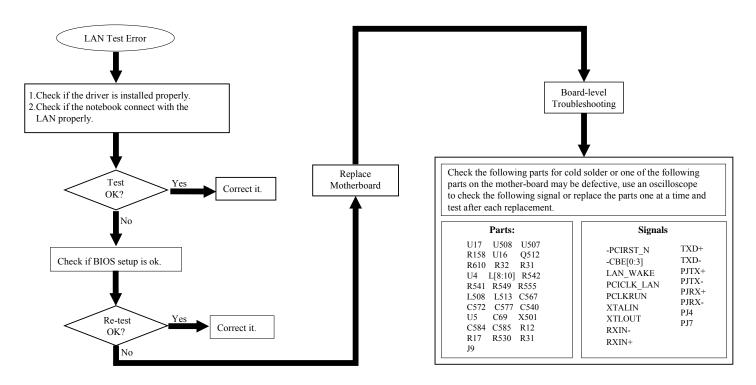

| 8.15 LAN Test Failure                                  | í |

| 9. Spare Parts List 178                                | 3 |

### **CONTENTS**

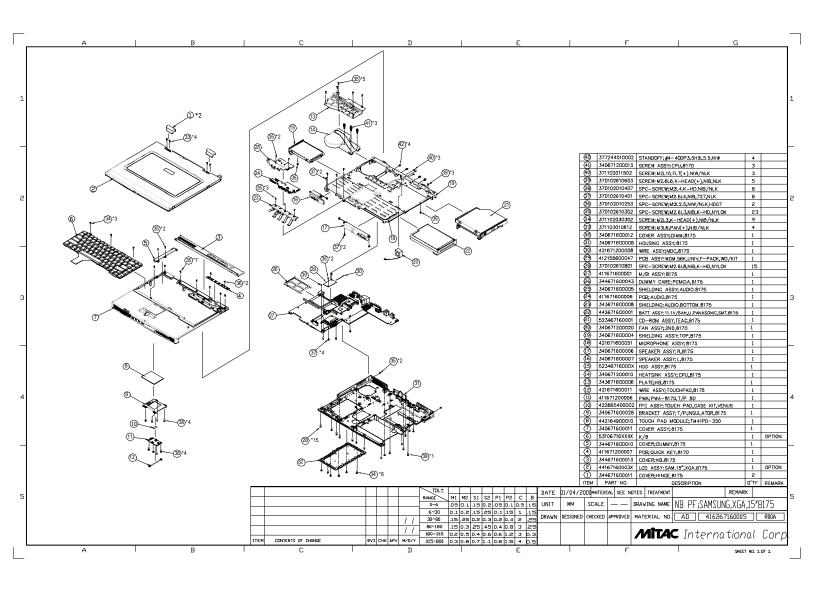

| 10. System Explode View | 190 |

|-------------------------|-----|

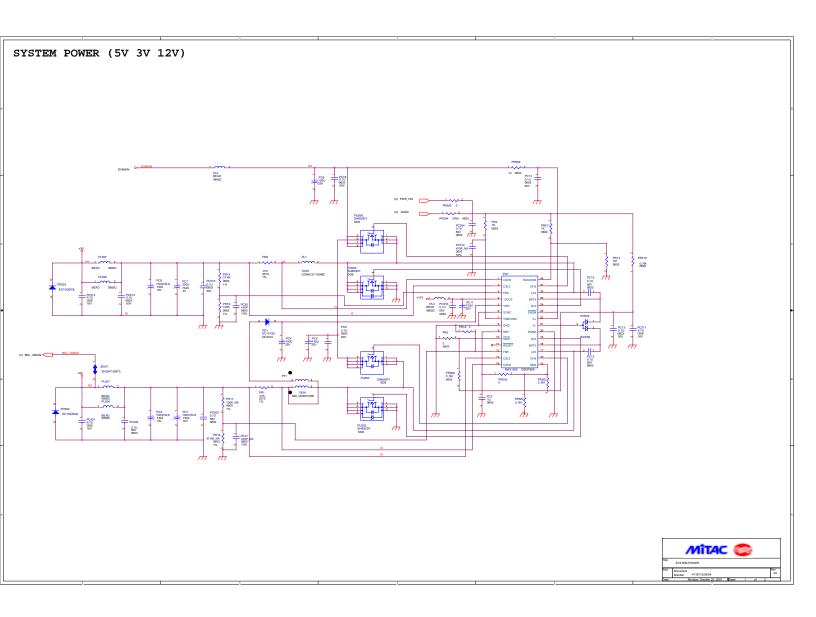

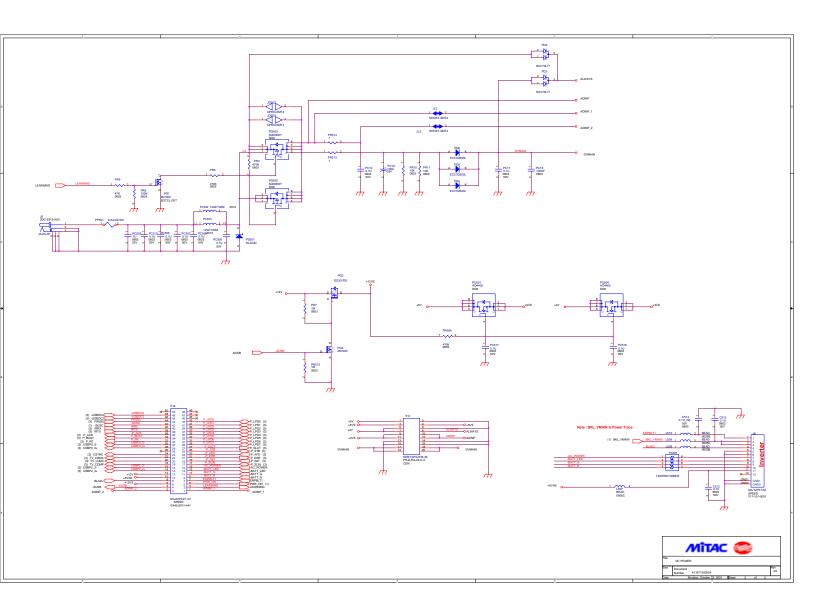

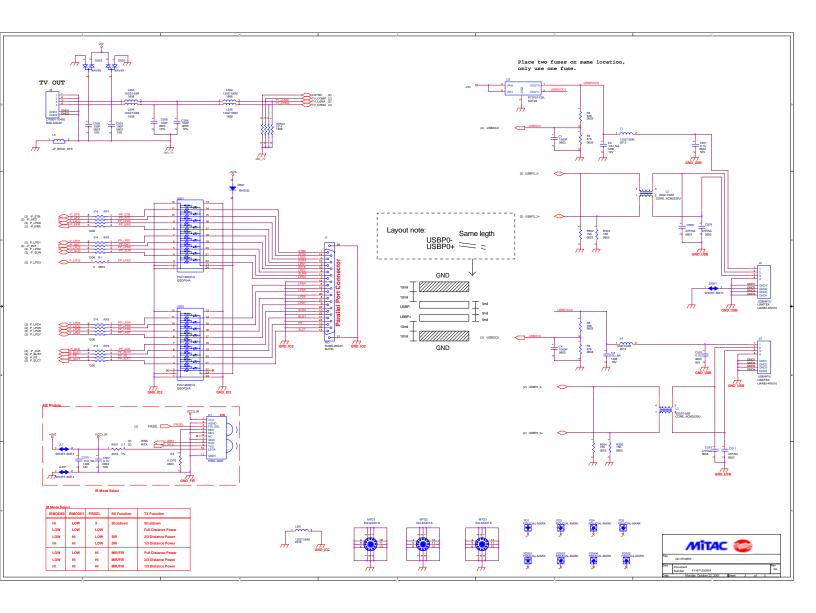

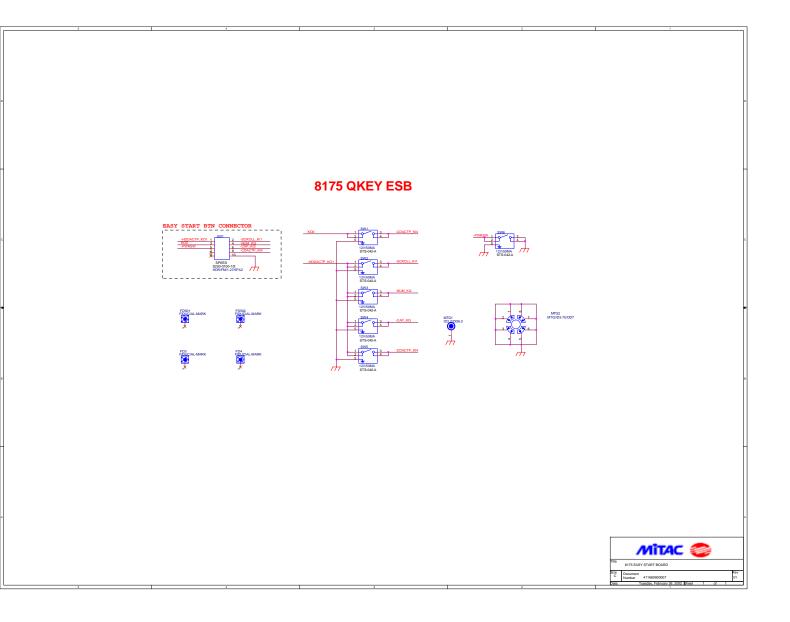

| 11. Circuit Diagram     | 191 |

| 12. Reference           | 218 |

,

## 1. Hardware Engineering Specification

### 1.1 Introduction

### 1.1.1 General Description

This document describes the system hardware engineering specification for 8175 portable notebook computer system. The 8175 notebook computer is a new mainstream high performance notebook in the MiTAC notebook family.

### 1.1.2 System Overview

| CPU         | mPGA 478 -PIN Socket Support Intel Pentium (Willamette)/Northwood in mFC-PGA2 package |  |  |

|-------------|---------------------------------------------------------------------------------------|--|--|

| Video       | . Dual independent Displays(LCD/CRT, LCD/TV,CRT/TV)                                   |  |  |

|             | Support Motion Compensation and iDCT                                                  |  |  |

|             | 3. Support Simultaneous display                                                       |  |  |

| Momory      | Two 144Pin SO-DIMM ,without and on-board Memory                                       |  |  |

| PCMCIA      | 1. Support one slot of TypeII                                                         |  |  |

|             | 2. Non Support Zoom video/Audio Function                                              |  |  |

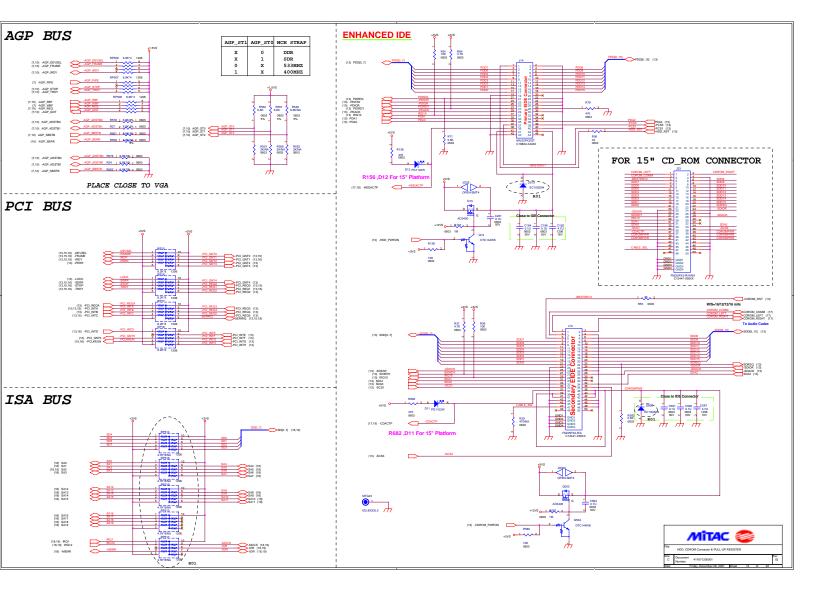

| IDE         | Support 2 IDE channel, Up to Ultra DMA 100                                            |  |  |

| LCD Display | Support Dual 85MHz LVDS interface.                                                    |  |  |

|             | Support up to sXGA+ (1400*1050) Resolution                                            |  |  |

| Button      | 5 Easy Start Button(functions defined by user)& 1 Mail Receive Button                 |  |  |

| LAN         | Support to 10/100 Based T                                                             |  |  |

| Modem       | 56Kbps V.90 MDC Modem                                                                 |  |  |

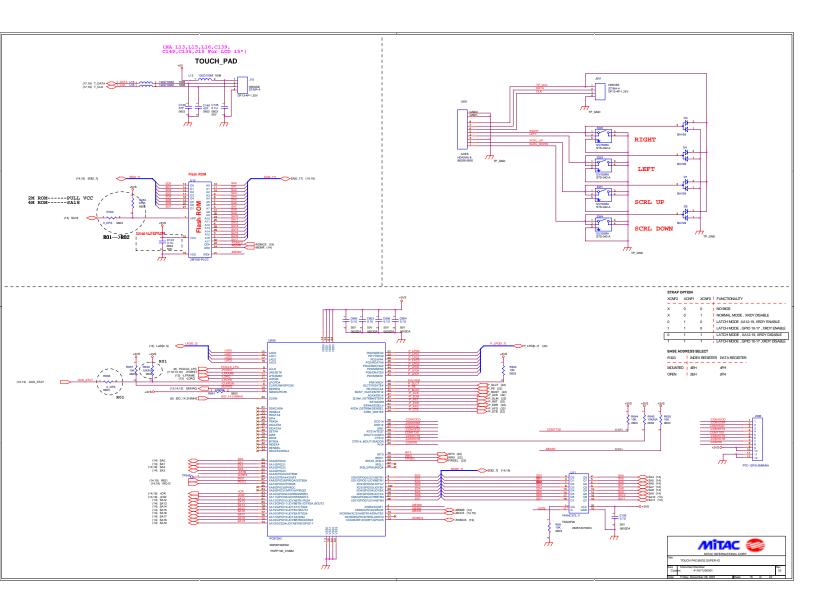

| Pointing    | Glide PAD with 2 Buttons and 1 scroll button                                          |  |  |

| Keyboard    | Internal Key Matrix Keyboard                                                          |  |  |

| BIOS        | 512KB Flash EEPROM (Include System BIOS&VGA BIOS)                                     |  |  |

| Audio        | 1. AC'97 Interface Codec. Sound Blaster Pro Compatible. |                                    |  |

|--------------|---------------------------------------------------------|------------------------------------|--|

|              | 2. Built-In 21W speaker and 1 Mono-Microphone           |                                    |  |

| I/O Port     | 1. Bi-Direction Parallel Port (EPP/ECP)                 | 2. External VGA Port(D-SUB 15Pins) |  |

|              | 3. 2 Standard USB 1.1 Port                              | 4. SPIDF Jack                      |  |

|              | 5. RJ-11 Port for Modem 6. Microphone In Jck            |                                    |  |

|              | 7. RJ-45 Port for LAN                                   | 8. VR for Audio Volume Control     |  |

|              | 9. DC Input Jack                                        | 10.Mini IEEE 1394 Port             |  |

|              | 11. S-Video Output Port(NTSC/PAL) 12. Battery Connector |                                    |  |

| Suspend Mode | POS(S1), Suspend to RAM(S3), Suspend to Disk(S4)        |                                    |  |

| Indicator    | HDD,FDD,CD-ROM,Num Lock,Caps Lock, Scroll Lock LEDs     |                                    |  |

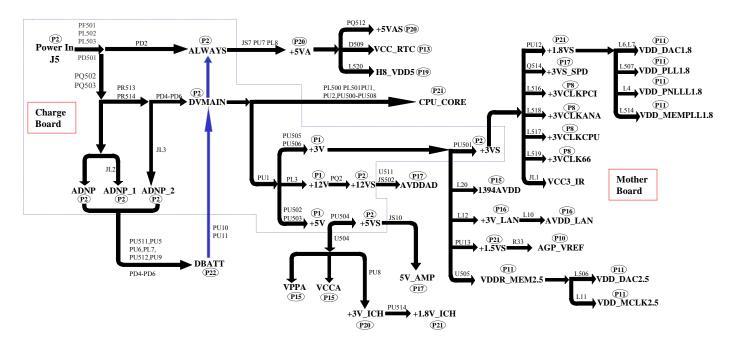

### 1.2 System Architecture

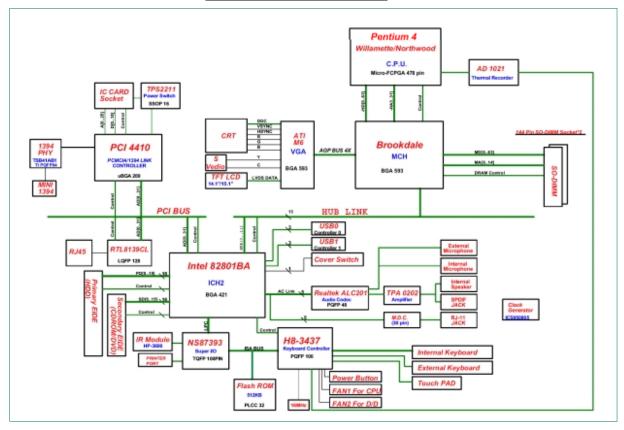

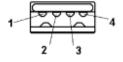

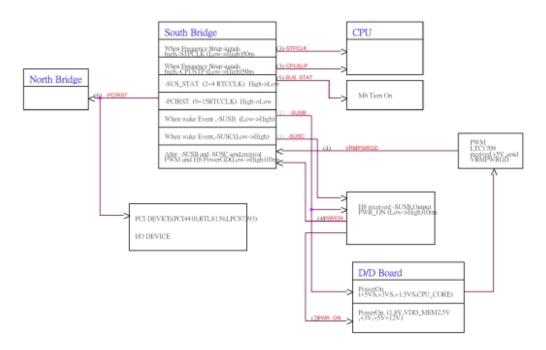

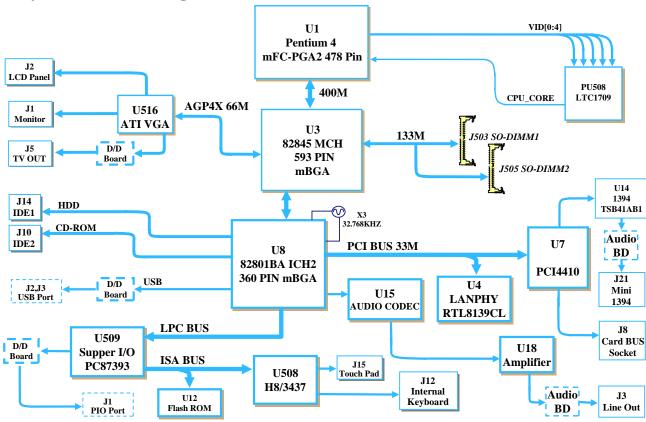

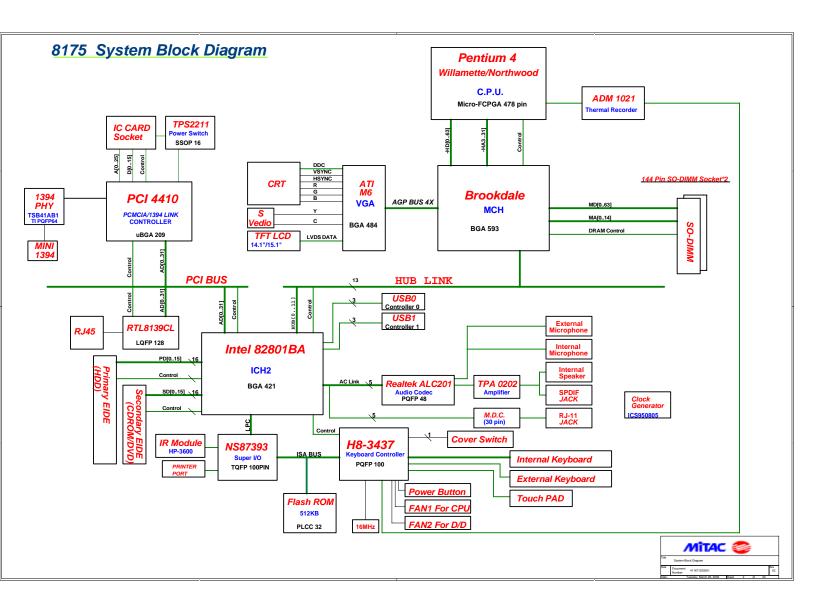

### 1.2.1 Block Diagram(without Power System)

\_

### 8175 System Block Diagram

#### 1.2.2 Function Description

#### 1.2.2.1 CPU

Socket Intel Pentium 4/ Northwood processors with 100MHz FSB.400MHz system bus. Capable of mFC-PGA2 package

- Available at 1.50, 1.60, 1.70, 1.80, 1.90 and 2 GHz

- Binary compatible with applications running on previous members of the Intel microprocessor line

- ♦ Intel® NetBurst™ micro-architecture

- System bus frequency at 400 MHz

- Rapid Execution Engine: Arithmetic Logic Units (ALUs) run at twice the processor core frequency

- Hyper Pipelined Technology

- Advance Dynamic Execution

- ---Very deep out-of-order execution

- ---Enhanced branch prediction

- ♦ Level 1 Execution Trace Cache stores 12K micro-ops and removes decoder latency from main execution loops

- ♦ 8 KB Level 1 data cache

- 256 KB Advanced Transfer Cache (on-die,full speed Level 2 (L2) cache) with 8-way associatively and Error Correcting Code (ECC)

- ♦ 144 new Streaming SIMD Extensions 2 (SSE2) instructions

- Enhanced floating point and multimedia unit for enhanced video, audio, encryption, and 3D performance

- Power Management capabilities

- ---System Management mode

- ---Multiple low-power states

,

- Optimized for 32-bit applications running on advanced 32-bit operating systems

- ♦ 8-way cache associatively provides improved cache hit rate on load/store operations.

#### **1.2.2.2 CORE LOGIC**

#### Intel Brookdale 82845 Memory Control HUB

- ♦ Intel® Pentium® 4 Processor (478 pin package) Support:

- ---Enhanced Mode Scaleable Bus Protocol

- ---2x Address, 4x Data

- ---System Bus interrupt delivery

- ---400 MHz system bus

- ---System Bus Dynamic Bus Inversion (DBI)

- ---32-bit system bus addressing

- ---12 deep In-Order Queue

- ---AGTL+ bus driver technology with integrated AGTL+ termination resistors

- System Memory Support

- ---Directly supports one SDR SDRAM channel, 64 bits wide (72 bits with ECC)

- ---133 MHz SDR SDRAM devices

- ---64 Mb, 128 Mb, 256 Mb and 512 Mb technologies for x8 and x16 devices

- ---By using 64 Mb technology, the smallest memory capacity possible is 32 MB

- ---Configurable optional ECC operation (single bit Error Correction and multiple bit Error Detection)

- --- Page sizes of 2 KB, 4 KB, 8 KB and 16 KB (individually selected for every row)

- ---Thermal management

- ---Maximum of 3 Double-Sided DIMMs (6rows populated) with unbuffered PC133 (with or without ECC)

- --- 3 GB Maximum using 512 Mb technology

- ---Supports up to 24 simultaneous open pages

- --- Maximum memory bandwidth of 1.067 GB/s with PC133

- ♦ Hub Interface to Intel® 82801BA ICH2

- ---266 MB/s point-to-point hub interface to ICH2

- ---66 MHz base clock

- ---MSI interrupt messages, power management state change, SMI, SCI and SERR error indication

- Accelerated Graphics Port (AGP) Interface

- --- Supports a single AGP device (either a connector or on the motherboard)

- ---Supports AGP 2.0 including 1x, 2x, and 4x AGP data transfers and 2x/4x Fast Write protocol

- ---Supports only 1.5 V AGP electrical characteristics

- ---32 deep AGP request queue

- ---Delayed transaction support for AGP-to-System Memory FRAME# semantic reads

- ♦ System Interrupt Support

- ---System bus interrupt delivery mechanism

- ---Interrupts signaled as upstream memory writes from AGP/PCI

- ---Supports peer MSI between hub interface and AGP

- ---Provides redirection for IPI and upstream interrupts to the system bus

- Power Management

- ---SMRAM space remapping to A0000h

- ---Supports extended SMRAM space above 256 MB, additional TSEG from Top of Memory

- interface are not supported

- ---PC '99 suspend to DRAM support

- --- ACPI, Revision 1.0b compliant power management

- ---APM, Revision 1.2 compliant power management

- ---NT Hardware Design Guide, Version 1.0 compliant

- Package

- ---MCH: 593 pin FC-BGA (37.5 x 37.5 mm)

#### Intel 82801BA Internal Connect HUB

- ♦ PCI Bus I/F

- ---Supports PCI at 33 MHz

- ---Supports PCI Rev 2.2 Specification

- ---133 MByte/sec maximum throughput

- ---Supports up to 6 master devices on PCI

- ---One PCI REQ/GNT pair can be given higher arbitration priority (intended for external 1394 host controller)

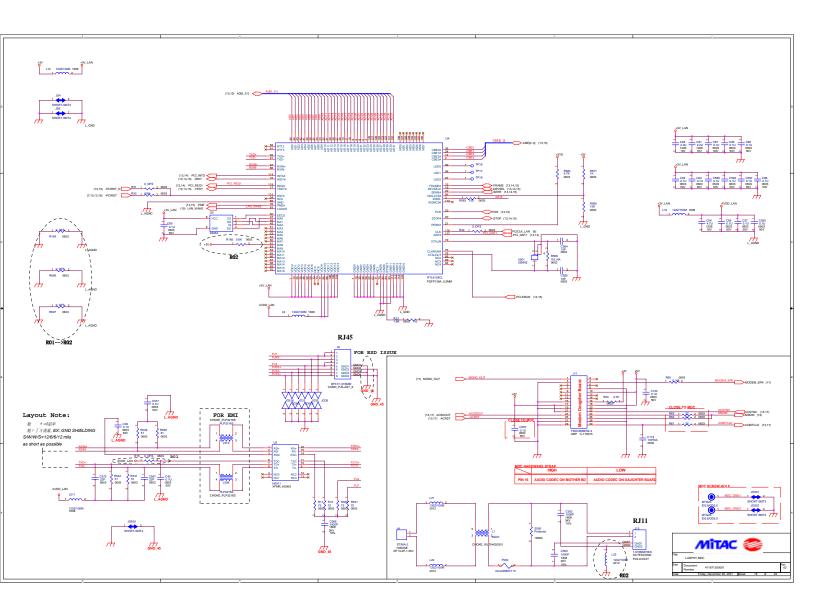

- Integrated LAN Controller

- ---WfM 2.0 Compliant

- ---Interface to discrete LAN Connect component

- ---10/100 Mbit/sec Ethernet support

- --- 1 Mbit/sec HomePNA\* support

- ♦ Integrated IDE Controller

- ---Independent timing of up to 4 drives

- ---Ultra ATA/100/66/33, BMIDE and PIO modes

- Read transfers up to 100MB/s, Writes to 89 MB/s

- ---Separate IDE connections for Primary and Secondary cables

- ---Implements Write Ping-Pong Buffer for faster write performance

- USB

- ---2 UHCI Host Controllers with a total of 4 ports

- ---USB 1.1 compliant

- ---Supports wake-up from sleeping states S1-S4

- ---Supports legacy Keyboard/Mouse software

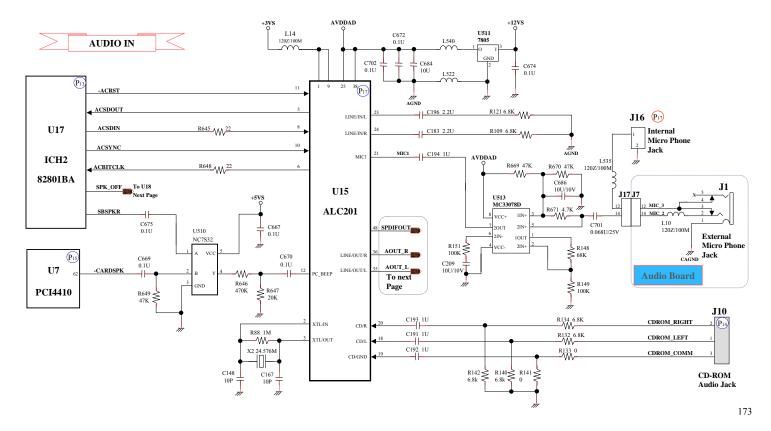

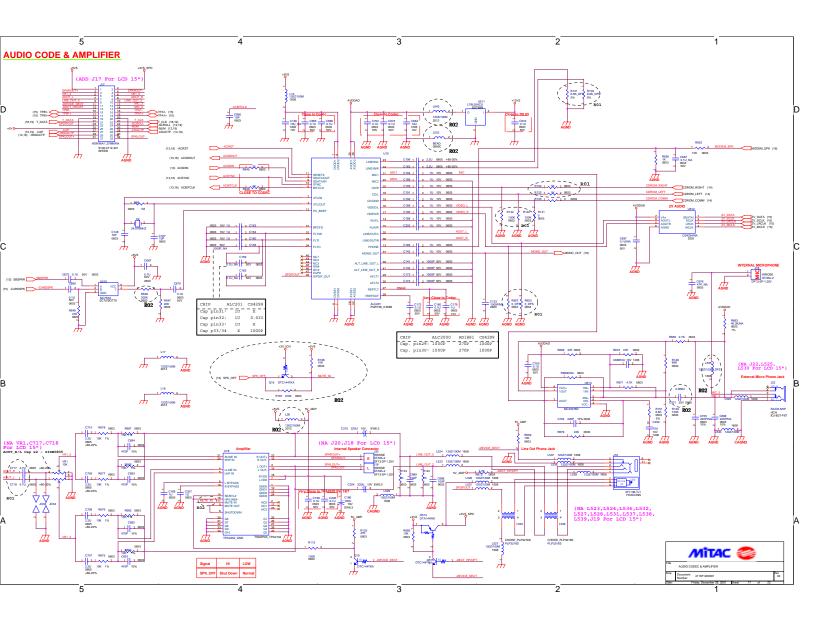

- ♦ AC'97 Link for Audio and Telephony CODECs

- ---AC'97 2.1 compliant

- ---Independent bus master logic for 5 channels (PCM In/Out, Mic Input, Modem In/Out)

- ---Separate independent PCI functions for Audio and Modem

- ---Support for up to six channels of PCM audio output (full AC3 decode)

- ---Supports wake-up events

- Interrupt Controller

- ---Support up to 8 PCI interrupt pins

- ---Supports PCI 2.2 Message-Based Interrupts

- ---Two cascaded 82C59

- ---Integrated I/O APIC capability

- ---15 interrupts supported in 8259 mode, 24 supported in I/O APIC mode

- ---Supports Serial Interrupt Protocol

- ---Supports Front-Side Bus interrupt delivery

- ♦ 1.8 V operation with 3.3 V I/O

- ---5V tolerant buffers on IDE, PCI, USB Over current and Legacy signals

- GPIO

- ---TTL, Open-Drain, Inversion

- ♦ Timers Based on 82C54

- ---System timer, Refresh request, Speaker tone output

- Power Management Logic

- ---ACPI 1.0 compliant

- ---ACPI Power Management Timer

- ---PCI PME# support

- ---SMI# generation

- ---All registers readable/restorable for proper resume from 0V suspend states

- ---Support for APM-based legacy power management for non-ACPI implementations

- External Glue Integration

- ---Integrated Pull-up, Pull-down and Series Termination resistors on IDE and processor interface

- Enhanced Hub I/F buffers improve routing flexibility (Not available with all Memory Controller Hubs)

- ♦ Firmware Hub (FWH) I/F supports BIOS memory size up to 8 MBs

- ♦ Low Pin count (LPC) I/F

- ---Allows connection of legacy ISA and X-Bus devices such as Super I/O

- ---Supports two Master/DMA devices.

- Enhanced DMA Controller

- --- Two cascaded 8237 DMA controllers

- ---PCI DMA: Supports PC/PCI Includes two PC/PCI REQ#/GNT# pairs

- ---Supports LPC DMA

- ---Supports DMA Collection Buffer to provide Type-F DMA performance for all DMA channels

- Real-Time Clock

- ---256-byte battery-backed CMOS RAM

- ---Hardware implementation to indicate century rollover

- System TCO Reduction Circuits

- --- Timers to generate SMI# and Reset upon detection of system hang

- ---Timers to detect improper processor reset

- ---Integrated processor frequency strap logic

- SM Bus

- ---Host interface allows processor to communicate via SM Bus

- ---Slave interface allows an external Micro controller to access system resources

- ---Compatible with most 2-Wire components that are also I2C compatible

- Supports ISA bus via external PCI-ISA Bridge

- ♦ 360-pin EBGA package

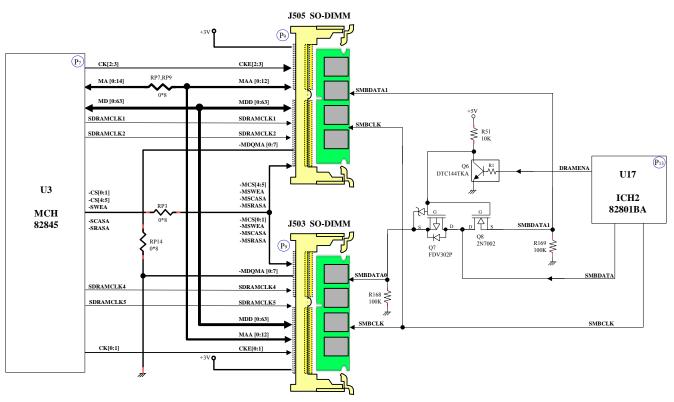

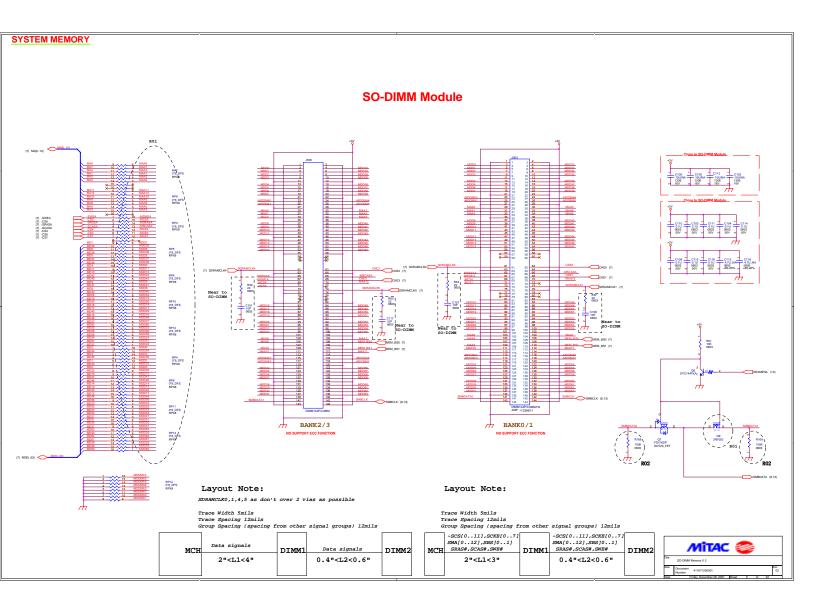

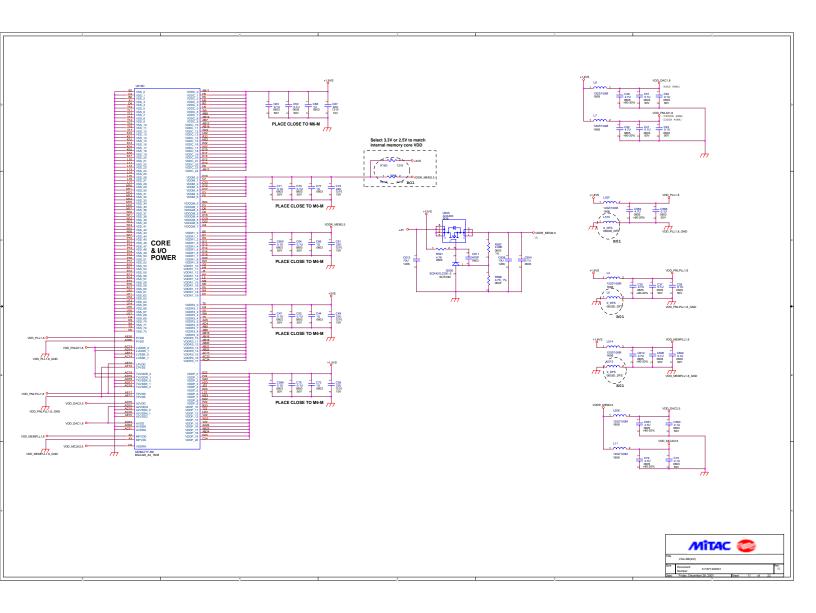

### 1.2.2.3 **Memory**

64MB PC133 SDRAM SO-DIMM Expandable to 1024MB(2 SODIMM slots). Support 3.3V PC133 SDR SDRAM only.

Table 1.1 MEMORY EXPANSION CAPACITY

| Slot1 | Slot2 | Total  |

|-------|-------|--------|

| 64MB  | 0     | 64MB   |

| 64MB  | 32MB  | 96MB   |

| 64MB  | 64MB  | 128MB  |

| 64MB  | 128MB | 192MB  |

| 64MB  | 256MB | 320MB  |

| 64MB  | 512MB | 576MB  |

| 128MB | 128MB | 256MB  |

| 128MB | 256MB | 384MB  |

| 128MB | 512MB | 640MB  |

| 256MB | 256MB | 512MB  |

| 256MB | 512MB | 768MB  |

| 512MB | 512MB | 1024MB |

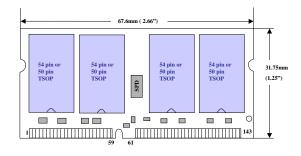

$\textbf{Figure 1.1} \underline{\textit{SO-DIMM MODULE}}$

#### 1.2.2.4 I/O Ports

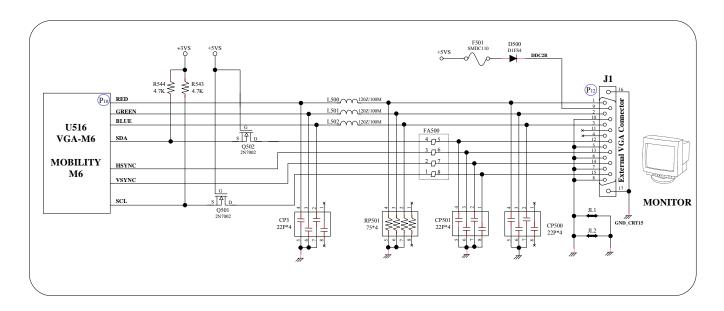

#### • CRT Port

- @ Standard VGA compatible port

- @ DDC1 and DDC2B compliant

Table 1.2

CRT CONNECTOR

| PIN | SIGNAL        | DESCRIPTION               |

|-----|---------------|---------------------------|

| 1   | RED           | Red analog video output   |

| 2   | GREEN         | Green analog video output |

| 3   | BLUE          | Blue analog video output  |

| 4   | Monitor Sense | Monitor Sense             |

| 5   | GND           | Ground                    |

| 6   | GND           | Ground                    |

| 7   | GND           | Ground                    |

| 8   | GND           | Ground                    |

| 9   | VCC           | +5VDC                     |

| 10  | GND           | Ground                    |

| 11  | Monitor Sense | Monitor Sense             |

| 12  | CRT DATA      | Data from DDC monitor     |

| 13  | HSYNC         | Horizontal Sync Control   |

| 14  | VSYNC         | Vertical Sync control     |

| 15  | CRT CLK       | Clock to DDC monitor      |

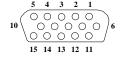

Figure 1.2 CRT CONNECTOR

#### • Standard 4 Pins S-VIDEO Port for TV-Out

- @ Support 1024\*768 resolution

- @ Support 848\*480 resolution in 16:9 mode

- @ Support PAL and NTSC system

Table 1.3 <u>S-VIDEO CONNECTOR</u>

| PIN | 1 | SIGNAL | DESCRIPTION |

|-----|---|--------|-------------|

| 1   |   | GND    | -           |

| 2   |   | GND    | -           |

| 3   |   | LUMA   | О           |

| 4   |   | CRMA   | О           |

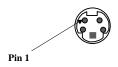

Figure 1.3 S-VIDEO Port

#### • IEEE1394 Port

Table 1.4 <u>IEEE1394 CONNECTOR</u>

| PIN | SIGNAL | DESCRIPTION |

|-----|--------|-------------|

| 1   | TPB-   | I/O         |

| 2   | TPB+   | I/O         |

| 3   | TPA-   | I/O         |

| 4   | TPA+   | I/O         |

Figure 1.4 <u>IEEE 1394 Port</u>

#### • AUDIO Ports

@ Built in 1 mono microphone, Built In 2 high quality internal speaker (1W)

- @ SPDIF

- @ Microphone In

#### • *RJ11*

@ Connection to Modem Daughter Board connector

Table 1.5 MODEM CONNECTOR

| PIN | SIGNAL NAME | DIRECTION | DESCRIPTION         |

|-----|-------------|-----------|---------------------|

| 1   | NC          | -         | No Connect          |

| 2   | LINE+       | I/O       | Phone Line Positive |

| 3   | LINE-       | I/O       | Phone Line Negative |

| 4   | NC          | -         | No Connect          |

Figure 1.5 MODEM Port

#### • RJ45

@ Connection to on-board NIC controller

Table 1.6 *LAN CONNECTOR*

| PIN | SIGNAL NAME | DIRECTION | DESCRIPTION                   |

|-----|-------------|-----------|-------------------------------|

| 1   | TX+         | Out       | Transmit Data Ring            |

| 2   | TX-         | Out       | Transmit Data Tip             |

| 3   | RX+         | IN        | Receive Data Ring             |

| 4   | TERM 1      | -         | Internal termination resistor |

| 5   | TEMR 2      | -         | Internal termination resistor |

| 6   | RX          | IN        | Receive Data Tip              |

| 7   | TERM 3      | -         | Internal termination resistor |

| 8   | TERM 4      | -         | Internal termination resistor |

Figure 1.6 <u>LAN CONNECTOR</u>

#### • USB Port

@ Two industry standard USB 1.1 ports

Table 1.7 USB Port2

| PIN | SIGNAL NAME | DIRECTION | DESCRIPTION              |

|-----|-------------|-----------|--------------------------|

| 1   | VCC         | -         | USB Device Power (+5VDC) |

| 2   | DATA-       | I/O       | Balanced Data Negaitve   |

| 3   | DATA+       | I/O       | Balanced Data Posiitve   |

| 4   | GND         | -         | Ground                   |

Figure 1.7 USB Port

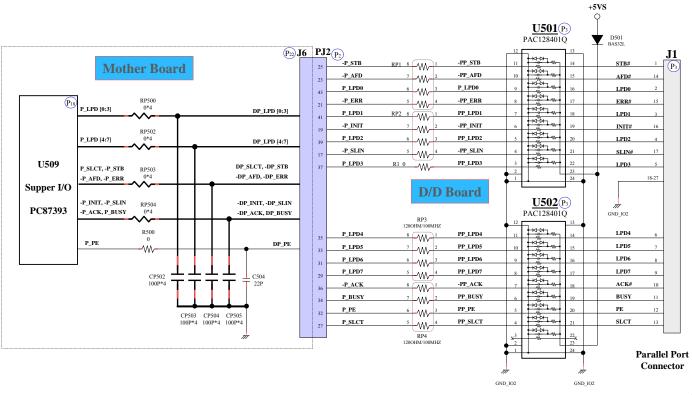

#### · Parallel Port

- @ Configurable as logical ports LPT1,LPT2 or LPT3

- @ EPP rev 1.7 & 1.9 compatible

- @ ECP(IEEE 1284) compatible

- @ Industry standard 25 Pins connector

Figure 1.8 PARALLEL PORT CONNECTOR

Table 1.8 PARALLEL Port

| PIN  | SIGNAL NAME | DIRECTION | DESCRIPTION              |

|------|-------------|-----------|--------------------------|

| 1    | STROBE#     | О         | Data Strobe              |

| 2    | PD0         | I/O       | PP Data bit 0            |

| 3    | PD1         | I/O       | PP Data bit 1            |

| 4    | PD2         | I/O       | PP Data bit 2            |

| 5    | PD3         | I/O       | PP Data bit 3            |

| 6    | PD4         | I/O       | PP Data bit 4            |

| 7    | PD5         | I/O       | PP Data bit 5            |

| 8    | PD6         | I/O       | PP Data bit 6            |

| 9    | PD7         | I/O       | PP Data bit 7            |

| 10   | -ACK        | I         | Printer Acknowledge      |

| 11   | BUSY        | I         | Printer Busy             |

| 12   | PE          | I         | Paper Out                |

| 13   | SLCT        | I         | Print Select Acknowledge |

| 14   | -AUTOFDXT   | О         | Auto Line Feed           |

| 15   | -ERROR      | I         | Printer Error            |

| 16   | -INIT       | О         | Reset Printer            |

| 17   | SLCTIN#     | I         | Select In                |

| 18   | GND         | -         | Ground                   |

| 19   | GND         | -         | Ground                   |

| 20   | GND         | -         | Ground                   |

| 21   | GND         | -         | Ground                   |

| 22   | GND         | -         | Ground                   |

| 23   | GND         | -         | Ground                   |

| 24   | GND         |           | Ground                   |

| 25   | GND         | -         | Ground                   |

| Case | GND         | -         | Ground                   |

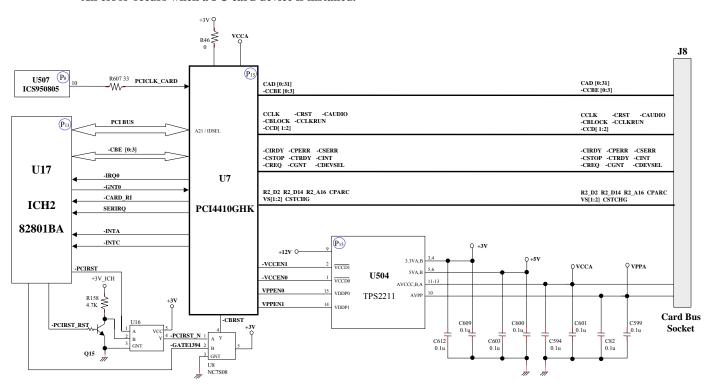

#### 1.2.2.5 PC CARD SLOT

- One Type II/I slot supporting the 1997 PC Card standard, and including full R2(16-bit) and 32-bit Card bus Data transfer

- ♦ TI PCI4410(PCMXCIA Controller)& TI TPS2211(Power Switch)

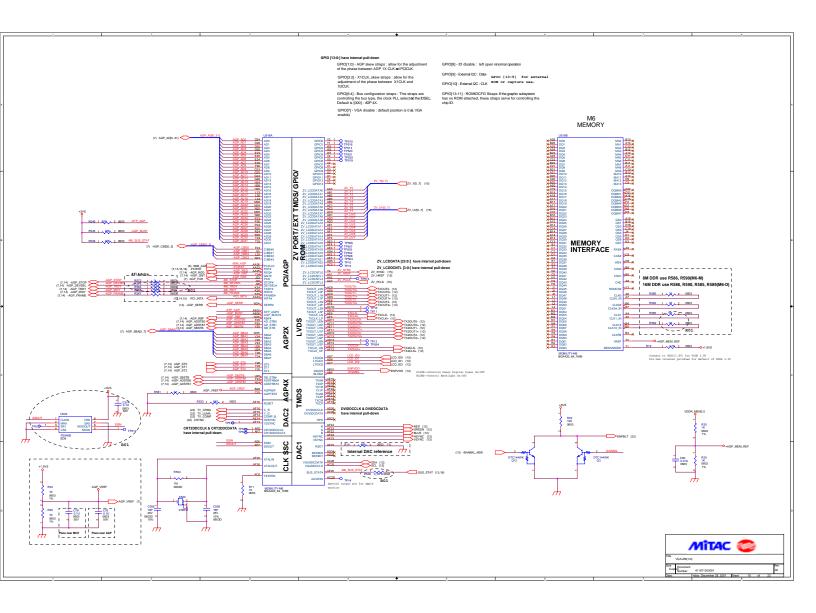

#### 1.2.2.6 GRAPHICAL SUBBSYSTEM

ATI Mobility M6 graphical controller embedded 8M DDR SDRAM

#### 1.2.2.7 **DISPLAY**

- ♦ Internal LCD Display is 14.1" TFT ISP XGA color

- External Video refresh rate of up to 100HZ support

- ---Vertical refresh frequencies to meet VESA requirements

- ---Simultaneous video in specified video modes-switchable with hot key

#### 1.2.2.8 READ ONLY MEMORY(BIOS FLASH)

- Fully compatible with industry standard software including windows 2000 & Windows XP

- ♦ Fully support APM V1.2 and latest ACPI specification

- 4Mb Flash BIOS

- Inside BIOS core

#### 1.2.2.9 POWER MANAGEMENT FEATURES

♦ Local standby mode(individual device such as HDD, graphics controller,LCD etc..)

- CPU Idle mode(including ACPI modes C1 and C2)

- Suspend mode(including S1 and S3 ACPI modes)

- ♦ Fully APM V1.2 compliant

- ♦ Fully ACPI V1.1 compliant

- ♦ Hibernate for Windows 2000 and windows XP

- ♦ Thermal management

- ♦ Fully US EPA Energy start compliant

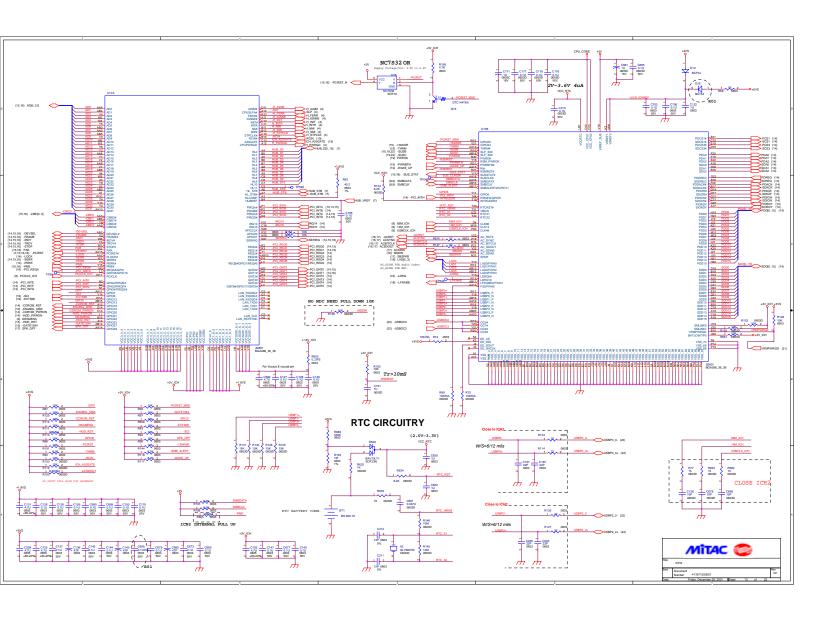

#### 1.2.2.10 KEYBOARD CONTROLLER

Hitachi H8-3437S

#### 1.2.2.11 SUPER I/O

♦ Ns PC87393F LPC interface Ultra I/O

#### 1.2.2.12 LEDS INDICATOR

♦ CDROM & HDD & NUM & CAP & SCROLL & EMIAL

#### **1.2.2.13 BUTTONS**

♦ FIVE PIECE EASY START RTN

#### 1.2.2.14 MODEM

Table 1.9 MODEM DAUGHTER BOARD CONNECTOR

| PIN | SIGNAL NAME | PIN | SIGNAL NAME    |

|-----|-------------|-----|----------------|

| 1   | MONO_OUT    | 2   | NC             |

| 3   | GND         | 4   | MODEM_SPK      |

| 5   | NC          | 6   | NC             |

| 7   | NC          | 8   | GND            |

| 9   | NC          | 10  | +5V            |

| 11  | NC          | 12  | NC             |

| 13  | NC          | 14  | NC             |

| 15  | GND         | 16  | Pull Up to +3V |

| 17  | +3V         | 18  | +5V            |

| 19  | GND         | 20  | GND            |

| 21  | +3V         | 22  | ACSYNC         |

| 23  | ACSDOUT     | 24  | MSDIN          |

| 25  | -ACRST      | 26  | MSDIN          |

| 27  | GND         | 28  | GND            |

| 29  | GND         | 30  | ACBITCLK       |

### 1.3 Electrical Characteristic

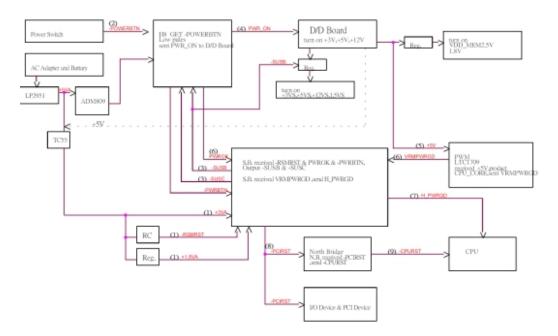

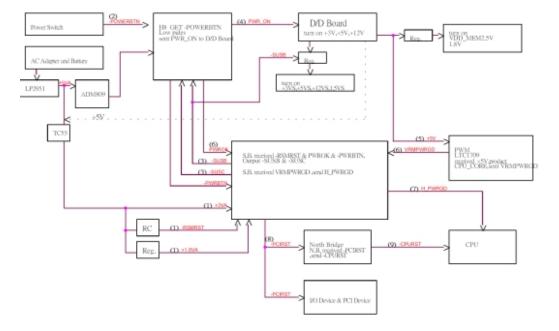

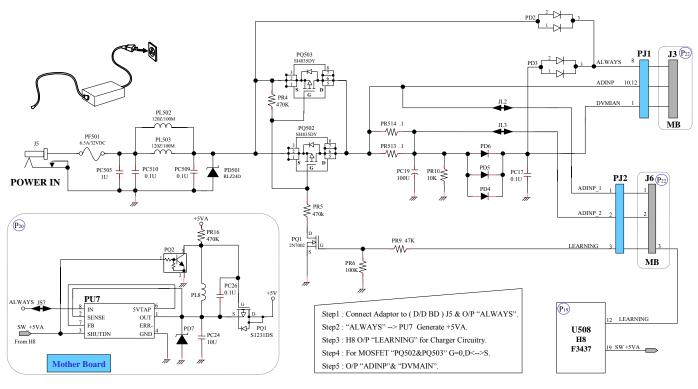

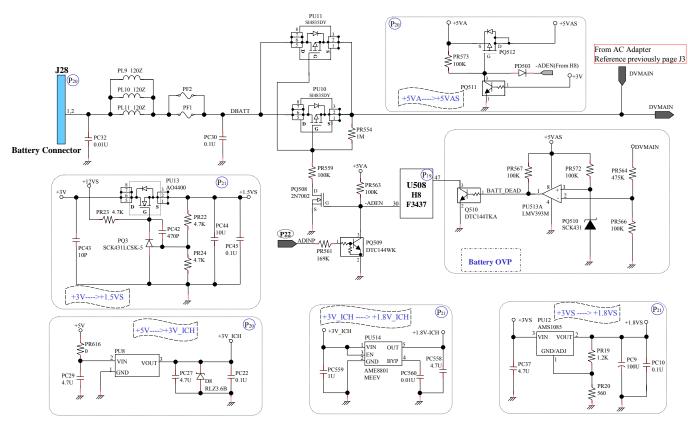

### 1.3.1 Power On Sequence

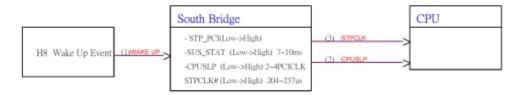

Figure 1.9 Power on Sequence

### 1.3.2 Power On Suspend Sequence

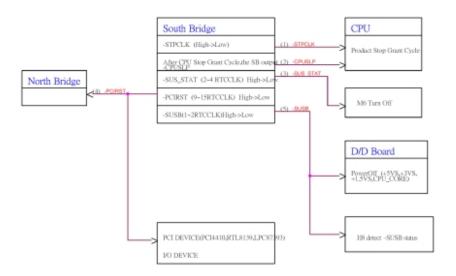

Figure 1.10 Power on Suspend Sequence

### 1.3.3 Resume from Power Suspend Sequence

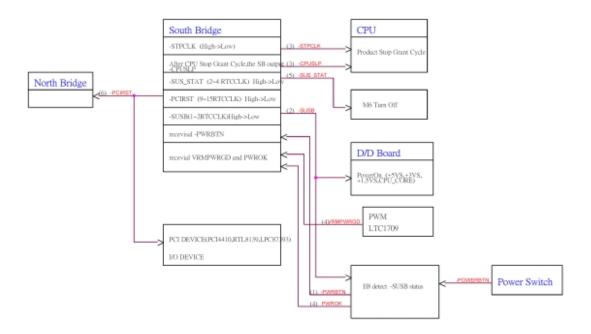

Figure 1.11 Resume from Power Suspend Sequence

### 1.3.4 Suspend to RAM Sequence

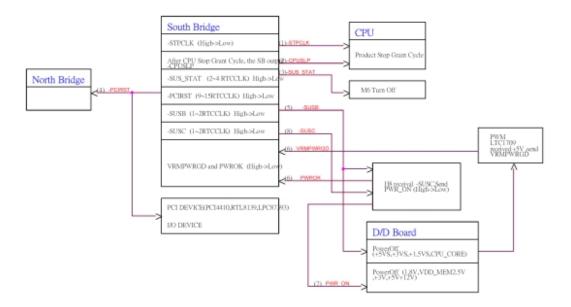

Figure 1.12 Suspend to RAM sequence

### 1.3.5 Resume from Suspend to RAM Sequence

Figure 1.13 Resume from Suspend to RAM Sequence

### 1.3.6 Suspend to Disk Sequence

Figure 1.14 Suspend to Disk Sequence

### 1.3.7 Resume from Suspend to Disk Sequence

Figure 1.15 Resume from Suspend to Disk Sequence

### 1.3.8 ICH2 GPI/O Pin Define

| Pin Name | Signal Name  | Power  | Type | During        | Immediately After | S1      | S3      | S4/S5   | Description            |

|----------|--------------|--------|------|---------------|-------------------|---------|---------|---------|------------------------|

|          |              |        |      | PCIRST#       | PCIRST#           |         |         |         |                        |

| GPIO0    | PULL-UP      | +3.3VS | I    | PC/PCI DEVICE |                   | DRIVEN  |         |         |                        |

| GPIO1    | PULL-UP      | +3.3VS | I    | PC/PCI DEVICE |                   | DRIVEN  |         |         |                        |

| GPIO2    | PULL-UP      | +3.3VS | X    | X             | X                 | X       | X       | X       | X                      |

| GPIO3    | PULL-UP      | +3.3VS | I    | HIGH-Z        | HIGH-Z            | HIGH-Z  |         |         |                        |

| GPIO4    | PULL-UP      | +3.3VS | I    | HIGH-Z        | HIGH-Z            | HIGH-Z  |         |         |                        |

| GPIO6    | PULL-UP      | +3.3VS | I    | MAIN I/O      |                   |         |         |         |                        |

| GPIO7    | PULL-UP      | +3.3VS | I    |               |                   |         |         |         |                        |

| GPIO8    | -SCI         | +3.3VA | I    |               |                   |         |         |         | ACPIMODE-SCI           |

| GPIO11   | PULL-UP      | +3.3VA | I    | HIGH-Z        | HIGH-Z            | DEFINED | DEFINED | DEFINED |                        |

| GPIO12   | -EXTSMI      | +3.3VA | I    |               |                   |         |         |         | DOS MODE -SMI          |

| GPIO13   | PULL-UP      | +3.3VA | I    |               |                   |         |         |         |                        |

| GPIO16   | TP           | +3.3VS | О    | HIGH-Z        | HI                | HI      | OFF     | OFF     |                        |

| GPIO17   | PULL-UP      | +3.3VS | О    | HIGH-Z        | HI                | HI      | OFF     | OFF     |                        |

| GPIO18   | PULL-UP      | +3.3VS | О    | HI            |                   | DEFINED | OFF     | OFF     |                        |

| GPIO19   | -ENABKL_MASK | +3.3VS | О    | HI            | HI                | DEFINED | OFF     | OFF     | MASK ENABLE            |

| GPIO20   | -CDROM_PWRON | +3.3VS | О    | HI            | HI                | DEFINED | OFF     | OFF     | Control CDROM Power on |

| GPIO21   | -HDD_PWRON   | +3.3VS | О    | HI            | HI                | DEFINED | OFF     | OFF     | Control HDD Power on   |

| GPIO22   | DRAMENA      | +3.3VS | О    | HIGH-Z        | HIGH-Z            | DEFINED | OFF     | OFF     | DRAM Data select       |

| GPIO23   | PULL-UP      | +3.3VS | OD   | LOW           | LOW               | DEFINED | OFF     | OFF     |                        |

| GPIO24   | -1394WR      | +3.3VA | О    | HIGH-Z        | HI                | DEFINED | DEFINED | DEFINED | 1394EEPROM R/W         |

| GPIO25   | -PCIRST_MSK  | +3.3VA | О    | HIGH-Z        | HI                | DEFINED | DEFINED | DEFINED | MASK PCIRST            |

| GPIO27   | -GATE1394    | +3.3VA | О    | HIGH-Z        | HI                | DEFINED | DEFINED | DEFINED | RST CARD BOARD         |

| GPIO28   | SPK_OFF      | +3.3VA | 0    | HIGH-Z        | HI                | DEFINED | DEFINED | DEFINED | OFF SPEAKER            |

### 1.3.9 Power Consumption Of Suspend Mode

- Suspend To RAM<TBD</p>

- Suspend To Disk/Soft-Off/Mechanical Off<TBD</p>

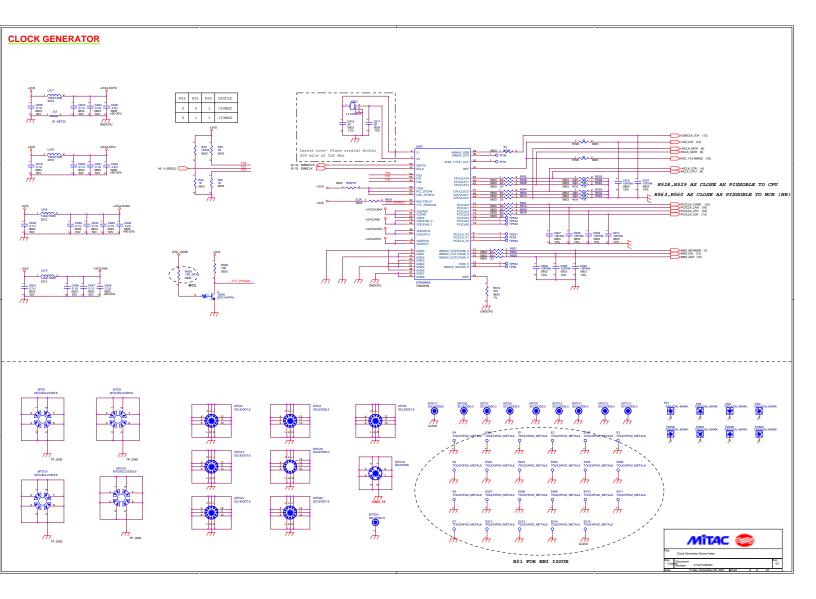

### 1.3.10 Clock Harmonic List

|    | Clock Harmonic |         |     |     |         |     |     |         |     |      |      |      |      |         |

|----|----------------|---------|-----|-----|---------|-----|-----|---------|-----|------|------|------|------|---------|

|    |                |         |     |     |         |     |     |         |     |      |      |      |      | Unit: M |

|    | 12.288         | 14.318  | 16  | 24  | 24.576  | 25  | 27  | 32.758  | 33  | 48   | 65   | 66   | 100  | 133     |

| 1  | 12.288         | 14.318  | 16  | 24  | 24.576  | 25  | 27  | 32.758  | 33  | 48   | 65   | 66   | 100  | 133     |

| 2  | 24.576         | 28.636  | 32  | 48  | 49.152  | 50  | 54  | 65.516  | 66  | 96   | 130  | 132  | 200  | 266     |

| 3  | 36.864         | 42.954  | 48  | 72  | 73.728  | 75  | 81  | 98.274  | 99  | 144  | 195  | 198  | 300  | 399     |

| 4  | 49.152         | 57.272  | 64  | 96  | 98.304  | 100 | 108 | 131.032 | 132 | 192  | 260  | 264  | 400  | 532     |

| 5  | 61.44          | 71.59   | 80  | 120 | 122.88  | 125 | 135 | 163.79  | 165 | 240  | 325  | 330  | 500  | 665     |

| 6  | 73.728         | 85.908  | 96  | 144 | 147.456 | 150 | 162 | 196.548 | 198 | 288  | 390  | 396  | 600  | 798     |

| 7  | 86.016         | 100.226 | 112 | 168 | 172.032 | 175 | 189 | 229.306 | 231 | 336  | 455  | 462  | 700  | 931     |

| 8  | 98.304         | 114.544 | 128 | 192 | 196.608 | 200 | 216 | 262.064 | 264 | 384  | 520  | 528  | 800  | 1064    |

| 9  | 110.592        | 128.862 | 144 | 216 | 221.184 | 225 | 243 | 294.822 | 297 | 432  | 585  | 594  | 900  | 1197    |

| 10 | 122.88         | 143.18  | 160 | 240 | 245.76  | 250 | 270 | 327.58  | 330 | 480  | 650  | 660  | 1000 | 1330    |

| 11 | 135.168        | 157.498 | 176 | 264 | 270.336 | 275 | 297 | 360.338 | 363 | 528  | 715  | 726  | 1100 | 1463    |

| 12 | 147.456        | 171.816 | 192 | 288 | 294.912 | 300 | 324 | 393.096 | 396 | 576  | 780  | 792  | 1200 | 1596    |

| 13 | 159.744        | 186.134 | 208 | 312 | 319.488 | 325 | 351 | 425.854 | 429 | 624  | 845  | 858  | 1300 | 1729    |

| 14 | 172.032        | 200.452 | 224 | 336 | 344.064 | 350 | 378 | 458.612 | 462 | 672  | 910  | 924  | 1400 | 1862    |

| 15 | 184.32         | 214.77  | 240 | 360 | 368.64  | 375 | 405 | 491.37  | 495 | 720  | 975  | 990  | 1500 | 1995    |

| 16 | 196.608        | 229.088 | 256 | 384 | 393.216 | 400 | 432 | 524.128 | 528 | 768  | 1040 | 1056 | 1600 | 2128    |

| 17 | 208.896        | 243.406 | 272 | 408 | 417.792 | 425 | 459 | 556.886 | 561 | 816  | 1105 | 1122 | 1700 | 2261    |

| 18 | 221.184        | 257.724 | 288 | 432 | 442.368 | 450 | 486 | 589.644 | 594 | 864  | 1170 | 1188 | 1800 | 2394    |

| 19 | 233.472        | 272.042 | 304 | 456 | 466.944 | 475 | 513 | 622.402 | 627 | 912  | 1235 | 1254 | 1900 | 2527    |

| 20 | 245.76         | 286.36  | 320 | 480 | 491.52  | 500 | 540 | 655.16  | 660 | 960  | 1300 | 1320 | 2000 | 2660    |

| 21 | 258.048        | 300.678 | 336 | 504 | 516.096 | 525 | 567 | 687.918 | 693 | 1008 | 1365 | 1386 | 2100 | 2793    |

| 22 | 270.336        | 314.996 | 352 | 528 | 540.672 | 550 | 594 | 720.676 | 726 | 1056 | 1430 | 1452 | 2200 | 2926    |

| 23 | 282.624        | 329.314 | 368 | 552 | 565.248 | 575 | 621 | 753.434 | 759 | 1104 | 1495 | 1518 | 2300 | 3059    |

| 24 | 294.912        | 343.632 | 384 | 576 | 589.824 | 600 | 648 | 786.192 | 792 | 1152 | 1560 | 1584 | 2400 | 3192    |

| 25 | 307.2          | 357.95  | 400 | 600 | 614.4   | 625 | 675 | 818.95  | 825 | 1200 | 1625 | 1650 | 2500 | 3325    |

| 26 | 319.488 | 372.268 | 416 | 624 | 638.976 | 650  | 702  | 851.708 | 858  | 1248 | 1690 | 1716 | 2600 | 3458 |

|----|---------|---------|-----|-----|---------|------|------|---------|------|------|------|------|------|------|

| 27 | 331.776 | 386.586 | 432 | 648 | 663.552 | 675  | 729  | 884.466 | 891  | 1296 | 1755 | 1782 | 2700 | 3591 |

| 28 | 344.064 | 400.904 | 448 | 672 | 688.128 | 700  | 756  | 917.224 | 924  | 1344 | 1820 | 1848 | 2800 | 3724 |

| 29 | 356.352 | 415.222 | 464 | 696 | 712.704 | 725  | 783  | 949.982 | 957  | 1392 | 1885 | 1914 | 2900 | 3857 |

| 30 | 368.64  | 429.54  | 480 | 720 | 737.28  | 750  | 810  | 982.74  | 990  | 1440 | 1950 | 1980 | 3000 | 3990 |

| 31 | 380.928 | 443.858 | 496 | 744 | 761.856 | 775  | 837  | 1015.5  | 1023 | 1488 | 2015 | 2046 | 3100 | 4123 |

| 32 | 393.216 | 458.176 | 512 | 768 | 786.432 | 800  | 864  | 1048.26 | 1056 | 1536 | 2080 | 2112 | 3200 | 4256 |

| 33 | 405.504 | 472.494 | 528 | 792 | 811.008 | 825  | 891  | 1081.01 | 1089 | 1584 | 2145 | 2178 | 3300 | 4389 |

| 34 | 417.792 | 486.812 | 544 | 816 | 835.584 | 850  | 918  | 1113.77 | 1122 | 1632 | 2210 | 2244 | 3400 | 4522 |

| 35 | 430.08  | 501.13  | 560 | 840 | 860.16  | 875  | 945  | 1146.53 | 1155 | 1680 | 2275 | 2310 | 3500 | 4655 |

| 36 | 442.368 | 515.448 | 576 | 864 | 884.736 | 900  | 972  | 1179.29 | 1188 | 1728 | 2340 | 2376 | 3600 | 4788 |

| 37 | 454.656 | 529.766 | 592 | 888 | 909.312 | 925  | 999  | 1212.05 | 1221 | 1776 | 2405 | 2442 | 3700 | 4921 |

| 38 | 466.944 | 544.084 | 608 | 912 | 933.888 | 950  | 1026 | 1244.8  | 1254 | 1824 | 2470 | 2508 | 3800 | 5054 |

| 39 | 479.232 | 558.402 | 624 | 936 | 958.464 | 975  | 1053 | 1277.56 | 1287 | 1872 | 2535 | 2574 | 3900 | 5187 |

| 40 | 491.52  | 572.72  | 640 | 960 | 983.04  | 1000 | 1080 | 1310.32 | 1320 | 1920 | 2600 | 2640 | 4000 | 5320 |

### 1.3.11 Audio Performance

♦ 8175 meet all the following items.

Table 1.10 Digital Playback (PC-D-A) for line Output

| Test Items                     | Mobile System         |

|--------------------------------|-----------------------|

| Full Scale Output Voltage      | >=0.7Vrms(3.3V audio) |

| Sample Frequency Accuracy      | <=0.1                 |

| Frequency Response(44.1ks/sec) | 20Hz~15Hz             |

| Frequency Response(48ks/sec)   | 20Hz~15Hz             |

| Dynamic Range(SNR)             | >=70dBFSA             |

| THD+N                          | <=-55dBFS             |

| Cross-talk                     | >=50dB                |

Table 1.11 Analog Pass-Through(A-A) for line input to line Output

| Test Items         | Mobile System |

|--------------------|---------------|

| Frequency Response | 20Hz~15kHz    |

| Dynamic Range(SNR) | >=70dBFSA     |

| THD+N              | <=-55dBFS     |

| Cross-talk         | >=50dB        |

Table 1.12 Analog Pass-Through(A-A) for Microphone input to line Output

| Test Items         | Mobile System |

|--------------------|---------------|

| Frequency Response | 100Hz~12kHz   |

| Dynamic Range(SNR) | >=60dBFSA     |

| THD+N              | <=-50dBFS     |

Table 1.13 <u>Digital Recording(A-D-PC) for Microphone input</u>

| Test Items                      | Mobile System |

|---------------------------------|---------------|

| Full Scale Input Voltage        | >=100mVrms    |

| Sample Frequency Accuracy       | <=0.1%        |

| Frequency Response(22.05ks/sec) | 100Hz~8.8kHz  |

| Dynamic Range(SNR)              | >=60dBFSA     |

| THD+N                           | <=-50dBFS     |

### 1.4 APPENDIX

#### APPENDIX A WILLAMETTE CPU CORE FEQUENCY SELECTION

| <b>Bus Ratio</b> | Core Freq | LINT[1]#NMI | A20M# | IGNNE# | LINT[0]#/INTR |

|------------------|-----------|-------------|-------|--------|---------------|

| 1/8              | 800MHz    | Н           | Н     | Н      | Н             |

| 1/10             | 1.00GHz   | Н           | Н     | L      | Н             |

| 1/11             | 1.10GHz   | Н           | Н     | L      | L             |

| 1/12             | 1.2GHz    | Н           | L     | Н      | Н             |

| 1/13             | 1.3GHz    | Н           | L     | Н      | L             |

| 1/14             | 1.4GHz    | Н           | L     | L      | Н             |

| 1/15             | 1.5GHz    | Н           | L     | L      | L             |

| 1/16             | 1.6GHz    | L           | Н     | Н      | Н             |

| 1/17             | 1.7GHz    | L           | Н     | Н      | L             |

| 1/18             | 1.8GHz    | L           | Н     | L      | Н             |

| 1/19             | 1.9GHz    | L           | Н     | L      | L             |

| 1/20             | 2.0GHz    | L           | L     | Н      | Н             |

| 1/21             | 2.1GHz    | L           | L     | Н      | L             |

| 1/22             | 2.2GHz    | L           | L     | L      | Н             |

| 1/23             | 2.3GHz    | Н           | Н     | Н      | L             |

| 1/24             | 2.4GHz    | L           | L     | L      | L             |

#### APPENDIX B CPU CORE VOLTAGE INDENTIFICATION DEFFINITION

| VID4 | VID3 | VID2 | VID1 | VID0 | Vcc max        |

|------|------|------|------|------|----------------|

| 1    | 1    | 1    | 1    | 1    | VRM output off |

| 1    | 1    | 1    | 1    | 0    | 1. 100         |

| 1    | 1    | 1    | 0    | 1    | 1. 125         |

| 1    | 1    | 1    | 0    | 0    | 1. 150         |

| 1    | 1    | 0    | 1    | 1    | 1. 175         |

| 1    | 1    | 0    | 1    | 0    | 1. 175         |

| 1    | 1    | 0    | 0    | 1    | 1. 225         |

|      | 1    | 0    | 0    | 0    |                |

| 1    | 0    |      | 1    | 1    | 1. 250         |

| 1    | - 1  | 1    |      | _    | 1. 275         |

| 1    | 0    | 1    | 1    | 0    | 1.300          |

| 1    | 0    | 1    | 0    | 1    | 1. 325         |

| 1    | 0    | 1    | 0    | 0    | 1. 350         |

| 1    | 0    | 0    | 1    | 1    | 1. 375         |

| 1    | 0    | 0    | 1    | 0    | 1.400          |

| 1    | 0    | 0    | 0    | 1    | 1. 425         |

| 1    | 0    | 0    | 0    | 0    | 1. 450         |

| 0    | 1    | 1    | 1    | 1    | 1. 475         |

| 0    | 1    | 1    | 1    | 0    | 1.500          |

| 0    | 1    | 1    | 0    | 1    | 1. 525         |

| 0    | 1    | 1    | 0    | 0    | 1.550          |

| 0    | 1    | 0    | 1    | 1    | 1. 575         |

| 0    | 1    | 0    | 1    | 0    | 1.600          |

| 0    | 1    | 0    | 0    | 1    | 1.625          |

| 0    | 1    | 0    | 0    | 0    | 1.650          |

| 0    | 0    | 1    | 1    | 1    | 1. 675         |

| 0    | 0    | 1    | 1    | 0    | 1. 700         |

| 0    | 0    | 1    | 0    | 1    | 1. 725         |

| 0    | 0    | 1    | 0    | 0    | 1. 750         |

| 0    | 0    | 0    | 1    | 1    | 1. 775         |

| 0    | 0    | 0    | 1    | 0    | 1. 800         |

| 0    | 0    | 0    | 0    | 1    | 1.825          |

| 0    | 0    | 0    | 0    | 0    | 1. 850         |

#### APPENDIX C FREQUENCY TABLE FOR BCLK[1:0]

| BSEL1 | BSEL0 | Function |

|-------|-------|----------|

| L     | L     | 100MHZ   |

| L     | Н     | RSV      |

| Н     | L     | RSV      |

| Н     | Н     | RSV      |

### LCD CABLE REQUIREMENT

- lacktriangle Each differential pair need meet maximum in impedance  $100\Omega$

- lacktriangle DC impedance have to meet maximum impedance 5m  $\Omega$  in each line

## HannStar LCD Cable Pin Define HSD150PX11-B

| Signal name | M/B Pin Number | LCD module pin number |

|-------------|----------------|-----------------------|

| LCDVCC      | 1              | 1                     |

| LCDVCC      | 2              | 2                     |

| GND         | 3              | 3                     |

| GND         | 4              | 4                     |

| GND         | 5              | 7                     |

| GND         | 6              | 10                    |

| TX2CLK+     | 7              | NC                    |

| TXCLK+      | 8              | 15                    |

| TX2CLK-     | 9              | NC                    |

| TRCLK-      | 10             | 14                    |

| GND         | 11             | 13                    |

| GND         | 12             | 16                    |

| TX2OUT0+ | 13 | NC |

|----------|----|----|

| TX2OUT1+ | 14 | NC |

| TX2OUT0- | 15 | NC |

| TX2OUT1- | 16 | NC |

| GND      | 17 | NC |

| GND      | 18 | NC |

| TX2OUT2+ | 19 | NC |

| TXOUT0+  | 20 | 6  |

| TX2OUT2- | 21 | NC |

| TXOUT0-  | 22 | 5  |

| GND      | 23 | 19 |

| GND      | 24 | 20 |

| TXOUT2+  | 25 | 12 |

| TXOUT1+  | 26 | 9  |

| TXOUT2-  | 27 | 11 |

| TXOUT1-  | 28 | 8  |

| GND      | 29 | NC |

| GND      | 30 | NC |

| LCD_ID0  | 31 | NC |

| +3VS     | 32 | NC |

| LCD_ID1  | 33 | NC |

| +3VS     | 34 | NC |

| LCD_ID2  | 35 | NC |

| +3VS     | 36 | NC |

| NC       | 37 | NC |

| NC       | 38 | NC |

| NC       | 39 | NC |

| NC       | 40 | NC |

| Display                        | Link Pin        |

|--------------------------------|-----------------|

| HannStar 15" TFT: HSD150PX11-B | (33&34) (35&36) |

# Sumsuang LCD Cable Pin Define LTN150P1-L03

| Signal name | M/B pin Number | LCD module pin number |

|-------------|----------------|-----------------------|

| LCDVCC      | 1              | 1                     |

| LCDVCC      | 2              | 2                     |

| GND         | 3              | 3                     |

| GND         | 4              | 4                     |

| GND         | 5              | NC                    |

| GND         | 6              | NC                    |

| TX2CLK+     | 7              | 20                    |

| TXCLK+      | 8              | 12                    |

| TX2CLK-     | 9              | 19                    |

| TXCLK-      | 10             | 11                    |

| GND         | 11             | NC                    |

| GND         | 12             | NC                    |

| TX2OUT0+    | 13             | 14                    |

| TX2OUT1+    | 14             | 16                    |

| TX2OUT0-    | 15             | 13                    |

| TX2OUT1-    | 16             | 15                    |

| GND         | 17             | NC                    |

| GND         | 18             | NC                    |

| TX2OUT2+    | 19             | 18                    |

| TXOUT+   | 20 | 6  |

|----------|----|----|

| TX2OUT2- | 21 | 17 |

| TXOUT0-  | 22 | 5  |

| GND      | 23 | NC |

| GND      | 24 | NC |

| TXOUT2+  | 25 | 10 |

| TXOUT1+  | 26 | 8  |

| TXOUT2-  | 27 | 9  |

| TXOUT1-  | 28 | 7  |

| GND      | 29 | NC |

| GND      | 30 | NC |

| LCD_ID0  | 31 | NC |

| +3VS     | 32 | NC |

| LCD_ID1  | 33 | NC |

| +3VS     | 34 | NC |

| LCD_ID2  | 35 | NC |

| +3VS     | 36 | NC |

| NC       | 37 | NC |

| NC       | 38 | NC |

| NC       | 39 | NC |

| NC       | 40 | NC |

| DISPLAY               | Link Pin                |

|-----------------------|-------------------------|

| Sumsuang-15P1-L03_MIC | (31&32),(33&34),(35&36) |

# **LCD Panel ID Define Table**

| LCD Panel         | LCD_ID2 | LCD_ID1 | LCD_ID0 |

|-------------------|---------|---------|---------|

| Uniqae            | 0       | 0       | 1       |

| Hyundai           | 0       | 1       | 0       |

| HannStar          | 0       | 1       | 1       |

| Unipac(SXGA)      | 1       | 0       | 0       |

| HannStar(SXGA)    | 1       | 0       | 1       |

| HannStar(XGA)15"  | 1       | 1       | 0       |

| Sumsung(SXGA+)15" | 1       | 1       | 1       |

# 1.5 BIOS Specification

# 1.5.1 BIOS Feature

- @ Inside BIOS for Intel 845 + ICH2 chipset

- @ 512KB flash ROM

- @ ACPI 1.0b Compliant (S1, S3, S4, S4BIOS)

- @ Support APM 1.2 (POS, STR, STD)

- @ SMBIOS 2.3.1

- @ Support external 1.44MB USB Floppy

- @ Support DVD-ROM and CD-ROM

- @ Support Multi-boot function

- @ Plug & Play for Devices

- @ Support FIR

- @ Silence Boot with Logo customized

- @ Wake-up from USB

- @ Fast boot bypass RAM/Floppy/CDROM testing

- @ BIOS Lock function Add the BIOS lock string at shadow memory address F000:E0C2

- @ Support boot from Network

- @ Support CRISIS recovery

# 1.5.2 Component&Drives

Please refer to the chapter of Power Management for state definitions. For PCI and PnP terms, please refer to respective specifications

### 1.5.2.1 CPU

- @ Intel Pentium 4 Processors Willamette//Northwood, Support upto 1.7GHz, 400 Mhz FSB

- @ Pentium 4 with 256K L2 Cache

- @ 64Kbyte on-chip L1 Cache

- @ CPU's Power transition (Please refer to the chapter of Power Management for state definitions) When in G0/Full-On, CPU can be in C0/C1/C2.

When in G1(STR)/G2(STD)/G3(Mechanical Off) State, CPU power is removed.

### 1.5.2.2 Memory System

- @ Two SODIMM for SDRAM extension from 64MB to 512MB Pentium 4 with 256K L2 Cache

- @ 400MHz Host Bus, 33MHz PCI Bus, 133MHz Memory Clock

- @ Dynamically row power-down

- @ Support Auto-refresh and Self-refresh command

- @ Auto-detect CAS latency Programming

- @ Memory Auto-sizing

- @ 1/2/4 Bank SDRAM support, up to 4 page could open at any time

### 1.5.2.3 PCI Devices

#### @ USB

- ---4 USB port are built in SB chipset (only 2 are supported in this model)

- ---Wake up from USB device is supported on POS/STR

#### @ VGA

- ---LCD panel could be turn on/off via function hotkey, or Lid switch if users define "Blank LCD" on cover closed in SCU.

- --- When in G0/Full-On/Idle, VGA stays in D0 state, Panel stays on. However, if no VGA activities detected for a specific period defined in SCU, VGA will go to D1 state, and Panel will be turned off.

- ---When in G2/G3/STD/Soft-Off/Mechanical Off State, VGA and Panel are power off.

- --- When in G1/Standby, VGA stays in D2 state, Panel stays off, Hsync/Vsync is cut.

- ---When in G1/STR, VGA stays in D3 state, Panel stays off, Hsync/Vsync is cut, especially, Note: VRAM is shared on system DRAM, so no special circuit is provided for VRAM refresh when G1/STR.

# @ AUDIO

- ---When in G0/Full-On/Idle, Audio stays in D0 state

- ---When in G2/G3/STD/Soft-Off/Mechanical Off State, Audio is power off.

#### @ MODEM

- ---Ring wake-up supported in G1/Standby/Suspend states.

- ---When in G0/Full-On/Idle, Modem stays in D0 state

- ---When in G2/G3/STD/Soft-Off/Mechanical Off State, Modem is power off.

#### @ PMCIA(TI4410)

---PME# supported

- ---Ring wake-up supported in G1/Standby/Suspend states.

- ---When in G0/Full-On/Idle, PCMCIA stays in D0 state if PC card is inserted, and stays in D2 state once PC card is removed.

- ---When in G2/G3/STD/Soft-Off/Mechanical Off State, PCMCIA is power off.

- ---When in G1/Standby, PCMCIA stays in D1 state.

- ---When in G1/Suspend, PCMCIA stays in D3 state.

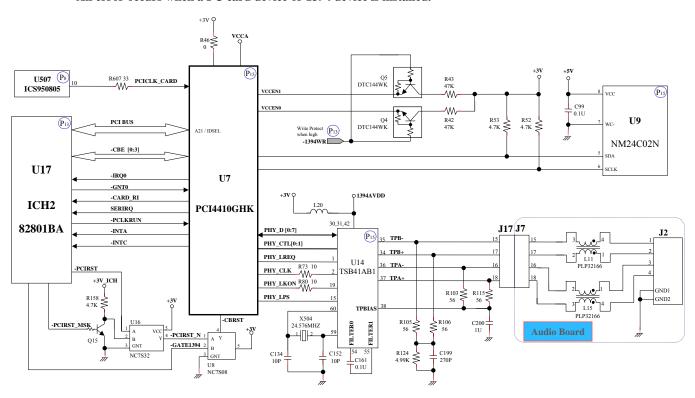

### @ IEE1394(TI4410)

--- PME# supported

### @ LAN(RTL8139CL)

- ---PME# supported

- ---Ring wake-up supported in G1/Standby/Suspend states.

#### **PCI Devices IDSEL**

| PCI Device | IDESL | Register Setting | Bus/ Device/ Function |

|------------|-------|------------------|-----------------------|

| Intel 845  |       |                  | 00 / 00 / 00          |

| P2P (NB)   |       |                  | 00 / 01 / 00          |

| P2P (SB)   | AD14  |                  | 00 / 30 / 00          |

| LPC Bridge | AD15  |                  | 00 / 31 / 00          |

| IDE        | AD15  |                  | 00 / 31 / 01          |

| USB #1     | AD15  |                  | 00 / 31 / 02          |

| SMB        | AD15  |                  | 00 / 31 / 03          |

| USB #2     | AD15  |                  | 00 / 31 / 04          |

| AC'97      | AD15  |                  | 00 / 31 / 05          |

| MC'97      | AD15  |                  | 00 / 31 / 06          |

| VGA        |       |                  | 01 / 00 / 00          |

| LAN        | AD18  |                  | 02 / 02 / 00          |

| PCMCIA     | AD19  |                  | 02/ 03 / 00           |

| IEEE 1394  | AD19  |                  | 02/ 03 / 01           |

### **PCI IRQ Routing**

| CI Device  | PIRQ A | PIRQ B | PIRQ C | PIRQ D | PIRQ H | PFA    | Bus/ Device/ |

|------------|--------|--------|--------|--------|--------|--------|--------------|

|            |        |        |        |        |        |        | Function     |

| Intel 845  |        |        |        |        |        | 0x0000 | 00 / 00 / 00 |

| P2P (NB)   |        |        |        |        |        | 0x0008 | 00 / 01 / 00 |

| P2P (SB)   |        |        |        |        |        | 0x00F0 | 00 / 30 / 00 |

| LPC Bridge |        |        |        |        |        | 0x00F8 | 00 / 31 / 00 |

| IDE        |        |        |        |        |        | 0x00F9 | 00 / 31 / 01 |

| USB #1     |        |        |        | INT D# |        | 0x00FA | 00 / 31 / 02 |

| SMB        |        |        |        |        |        | 0x00FB | 00 / 31 / 03 |

| USB #2     |        |        |        |        | INT C# | 0x00FC | 00 / 31 / 04 |

| AC'97      |        | INT B# |        |        |        | 0x00FD | 00 / 31 / 05 |

| MC'97      |        | INT B# |        |        |        | 0x00FE | 00 / 31 / 06 |

| VGA        | INT A# |        |        |        |        | 0x0100 | 01 / 00 / 00 |

| LAN        |        |        |        |        | INT A# | 0x0210 | 02 / 02 / 00 |

| PCMCIA     | INT A# |        |        |        |        | 0x0218 | 02/ 03 / 00  |

| IEEE 1394  |        |        | INT B# |        |        | 0x0219 | 02/ 03 / 01  |

# **1.5.2.4 ISA Device**

### @ Plug & Play Interface

- ---Plug and Play BIOS Spec. Rev. 1.0A Compliant

- ---No ESCD supported,

- ---No Docking Station Information supported

### @ RTC

- ---User could setup current date and time in SCU. RTC must be Y2K compliant

- ---User could also setup a RTC wake-up event at any time of a month.

### @ DMA

---ECP/FIR also use DMA but they are programmable

#### @ PIC

- ---IRQ0 is used by the system timer

- ---IRQ1 is used by KBC (Key Board Controller)

- ---IRQ2 is used by slave PIC

- ---IRQ3 is used by IR

- ---IRQ5 is used by Audio

- ---IRQ7 is used by LPT port

- ---IRQ8 is used by RTC (Real Time Clock)

- ---IRQ9 is shared by SCI

- ---IRQ10 is used by LAN

- ---IRQ10 is used by PCMCIA

- ---IRQ10 is used by IEEE 1394

- ---IRQ10 is also shared by VGA

- ---IRQ12 is used by mouse

- ---IRQ13 is used internally by CPU to recognize FPU interrupts

- ---IRQ14 is used by IDE channel 1

- ---IRQ15 is used by IDE channel 2

- ---Preserve two IRQs (4, 6, 11) for other devices to use.

#### @ Super I/O

- ---SIO chip could enter a full power down mode once system enter Suspend states

- ---Printer Port

Print port will enter power down mode when G1/G2/G3/STD/Suspend/Standby state.

---IR Port

IR port will enter power down mode and IR module's power will be cut off when G1/G2/G3/STD/ Suspend/Standby state.

#### @ KBC

---H8 will automatically control its power state. Please refer to KBC's specification

### **1.5.2.5 IDE Devices**

#### @ Hard Disk

- ---HD will enter standby mode whenever no access request is made.

- ---HD will enter standby mode when the system entering Standby state.

- ---HD will enter sleep mode when the system entering Suspend state.

#### @ CDROM

- ---CD drive will enter standby mode whenever no access request is made.

- ---CD drive enter standby mode when the system entering Standby state.

- ---CD drive enter sleep mode when the system entering Suspend state

### 1.5.2.6 AC'97 Device

- @ AC'97 Interface

- @ Audio Codec

- ---Enter the most power saving state during Suspend.

- @ Modem Codec

- ---Enter the most power saving state during Suspend

### 1.5.2.7 SMB

- (1) South Bridge SMB BUS

- @ SMBUS Device

| SMB Device | Read Addr | Write Addr |

|------------|-----------|------------|

| SDRAM 0    | 0xA1      | 0xA0       |

| SDRAM 1    | 0xA1      | 0xA0       |

| CLK_GEN    | 0xD3      | 0xD2       |

### @ SDRAM

- ---Use SMB link to read configuration data from SDRAM

- ---Turn off clock if no SO-DIMM insert automatically when POST

- @ Clock Generator

- ---Spread spectrum is enabled during POST

- (2) **H8 SMB BUS**

- @ Battery Pack

- ---This is polling by KBC (H8)

- @ Thermal Sensor

- ---Sensed by H8

- @ Charger

- ---Directly controlled by H8, please refer to KBC specification

### **1.5.2.8 Mechanics**

- @ Button

- ---1 Power Button, 5 Easy Start Buttons, 1 E-Mail Received Button.

- @ LID Switch

- ---See 1.6.7

- @ LEDs

- ---All LEDs are controller via H8, Please refer to H8 Specification

- @ FAN

- ---Controlled by H8

# 1.5.3 BIOS Setup

#### 1.5.3.1 Introduction

SCU allows you to configure the BIOS settings. Those settings are vital for your notebook to identify the types of installed devices as well as to utilize special features. Typical menu items include Date and Time, the types of disk drives, and IDE settings. Special features include Power Saving and Password settings The settings information is stored in the CMOS (Complementary Metal Oxide Semiconductor) RAM, which is powered by a RTC backup battery.

You may need to run SCU when

- \* You see an error message on the screen requesting you to run SCU

- \* You want to restore the factory default settings

- \* You want to modify some specific settings

# 1.5.3.2 Starting SCU

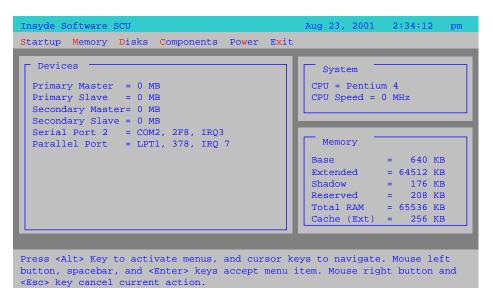

SCU is built into the system board. To run SCU, press [F2] during system startup. The main SCU screen appears as shown in Figure 1.15.

Figure 1.16 Main SCU Screen

#### The SCU screen can be divided into three areas:

- @ On the top line of the screen is the menu bar, which lists the titles of the available menus Each menu title contains a pull-down menu, which displays items for settings

- @ The middle section of the screen displays current settings of the system. If you open a pull-down menu and select an item that provides multiple options, a submenu will pop up and let you make further selections.

@ The bottom window provides alternative information. Normally it gives the keyboard/mouse instructions for moving around and making selections. When a menu item is highlighted, the window will provide more detailed description of the item.

### 1.5.3.3 Moving Around and Making Selections

You must go through two or three levels to complete the setting for an item. In most cases, there are three levels: menu title, pull-down menu, and submenu.

To move around and make selections, you can use both the touch pad/mouse and keyboard

#### **(2)** Using the Touch pad/Mouse

You are advised to use the touch pad or mouse. It is more straightforward than using the keyboard. For most items, simply move the pointer with the touch pad/mouse and left-click on the intended item. To cancel your selection, click the right button. For some items, you will need to select with the arrow keys.

#### @ Using the keyboard

Keyboard information can be found at the bottom of the screen. You can also use the shortcut key, which is highlighted in a different color on the screen.

Described below is the general procedure to complete a setting by use of the keyboard:

- ® Select a menu title with the left/right arrow key and press [Enter] to pull down the menu. You can directly pull down a menu You can directly pull down a menu by pressing [Alt] and the shortcut key.

- ® From the pull-down menu, select an item with the up/down arrow key and press [Enter] to access the submenu or change the setting, The submenu displays further options that you can select.

® For most menu items, pressing the [Tab] key will jump from one item to another, thus allowing you to go through the items quickly. To confirm the changes you make, press [Enter] or select the OK button. To cancel the changes, press [Esc] or select the Cancel button.

# 1.5.3.4 Startup Menu

The Startup pull-down menu, as shown below, contains some basic configuration and password settings of the system

#### Startup

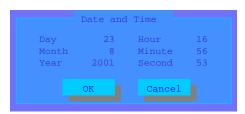

#### @ Data and time

The "Date and Time" item sets the system date and time. When this item is selected, the submenu will display as shown below:

### @ Splash Boot Logo

The "Splach boot Logo" item to enable or disable the big boot logo on screen when system is booting. When this item is selected, no submenu will display. A check mark ( $\sqrt{}$ ) indicates Enabled; an underline (\_) indicates Disabled. The default setting is Disabled

### @ Fast Boot

The "Fast Boot" item, when enabled, speeds up the booting procedure by bypassing the memory test. When this item is selected, no submenu will display. A check mark  $(\sqrt{})$  indicates Enabled; an underline  $(\underline{})$  indicates Disabled. The default setting is Enabled.

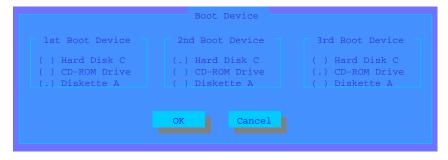

#### @ Boot Device

The "Boot Device" item sets the sequence of booting device. When this item is selected, the submenu will display as shown below.

The default setting is Diskette A, Hard Disk C, then CD-ROM Drive

NOTE: If you set all booting options to the same device (say, Hard Disk C), then the notebook will try to boot from that device only

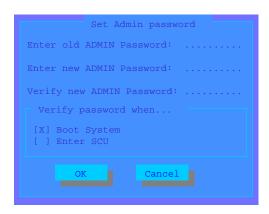

### @ Set Admin Password

This item lets you set up administrator-level password. When this item is selected, the submenu will display as shown below:

You can directly enter the new password if no password has previously existed. If a password has been previously set up, you have to enter the correct old password before setting up a new one. In either case, you have to enter the new password twice to complete the setting.

### **NOTE:**

- 1. If you want to clear a previous password, you can enter the old password and leave the following fields

- 2. The administrator password is required for booting and entering SCU, so the "Verify password when ..." setting can not be changed

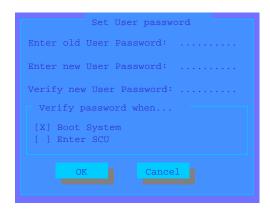

#### @ Set User Password

This item lets you set up user-level password. When this item is selected, the submenu will display as shown below:

The procedure to set up the user password is the same as "Set Admin Password".

### **\* NOTE:**

- 1. You can not set up the user password unless the administrator password has been set up.

- 2. If both the administrator and user passwords are set up, only one password is required to boot the system

- 3. To modify the SCU settings, you have to enter the administrator password. The user password only allows you to browse the settings.

- 4. If the "Resume System" item is checked, the password is required only when the system is restored from "Suspend-to-disk" status.

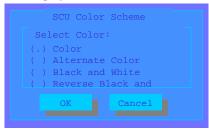

### @ SCU Color Scheme

The "Splach boot Logo" item select color set for your viewing. When this item is selected, the submenu will display as shown below:

The default setting is "Color".

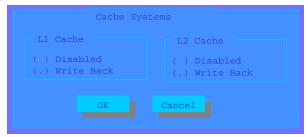

# 1.5.3.5 Memory Menu

Memory

Cache Systems >

### @ Cache System

The default settings of the "L1 Cache" and "L2 Cache" are "Write Back".

### **1.5.3.6 Disk Menu**

#### Disks

```

V Internal HDC

V IDE Setting >

Virus Alert >

```

### @ Internal HDC

The "Internal HDC" item sets if an internal hard drive is present.

When this item is selected, no submenu will display. A check mark  $(\sqrt{})$  indicates Enabled; an underline  $(\_)$  indicates Disabled

The default setting is Enabled

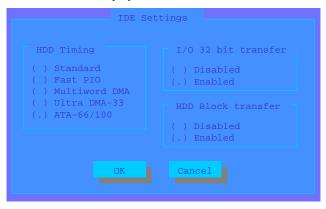

### @ IDE Setting

The "IDE Settings" item sets the type of the hard disk drive in your system. When this item is selected, the submenu will display as show below:

The "HDD Timing" item sets the data transmit mode of the hard drive. The default setting is Ultra DMA-33 The "I/O 32 bit transfer" item, if enabled, allows you to have better data transfer rate. This effect is more noticeable under DOS system. The default setting is Enabled

The "HDD Block transfer" item, if enabled, allows you to use hard disk with large capacity. The default setting is Enabled

### @ Virus Alert

The "Virus Alert" item, when enabled, gives warning messages if the hard disk boot sector (partition table) has been changed

When this item is selected, no submenu will display. A check mark ( $\sqrt{}$ ) indicates Enabled; an underline (\_) indicates disabled

The default setting is Disabled.

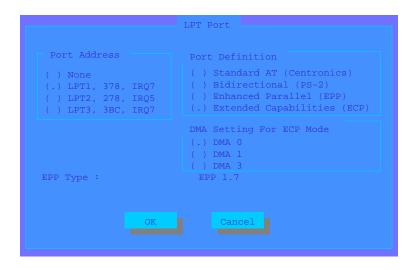

### 1.5.3.7 Components

#### **Components**

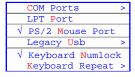

# @ COM Ports

The "COM Ports" item sets the settings of COM Port A and B. When this item is selected, the submenu will display as shown below:

COM B is assigned to IR function. You can further select the IR mode in "Mode Setting for COM B" item and DMA channel in "DMA Setting For Fast IR" when you select "Fast IR" in the mode setting.

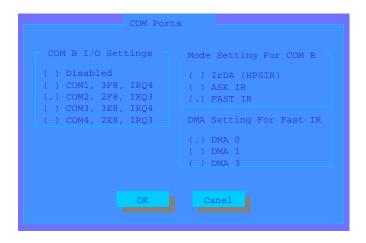

### @ LPT Ports

The "LPT Port" item sets the settings of LPT port. When this item is selected, the submenu will display as shown below:

Your system supports EPP (Enhanced Parallel Port) and ECP (Extended Capabilities Port) standards which turn the standard parallel port into a high speed bi-directional peripheral port. If you select ECP item, you can further choose which DMA channel to use.

### @ PS/2 Ports

The "PS/2 Mouse Port" item enables or disables the PS/2 mouse port

When this item is selected, no submenu will display. A check mark ( $\sqrt{}$ ) indicates Enabled; an underline (\_) indicates Disabled. The default setting is enabled.

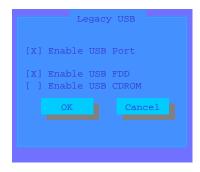

### @ Legacy USB

The "Legacy USB" item sets the settings of legacy USB port which enables or disables the USB keyboard, USB mouse, USB floppy and USB CD-ROM in DOS and SCU. When this item is selected, the submenu will display as shown below:

The "Enable USB Port" item enables or disables USB keyboard and USB mouse. The default setting is enabled

The "Enable USB FDD" item enables or disables USB FDD. The default setting is enabled.

The "Enable USB FDD" item enables or disables boot from USB CDROM. The default setting is disabled

### @ Keyboard Numlock

Keyboard Numlock" item sets if the numeric keypad will function

When this item is selected, no submenu will display. A check mark  $(\sqrt{})$  indicates Enabled; an underline (\_) indicates Disabled. The default setting is Enabled.

Note: If you disable this option, you can only activate the numeric keypad by holding down the [Fn] key first, even when the Num Lock indicator is on. However, an externally-connected keyboard is not affected by this feature.

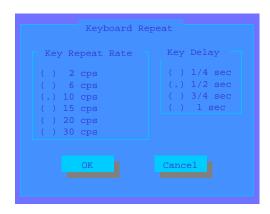

### @ Keyboard Repeat

The "Keyboard Repeat" item sets the repeat rate and delay time of key strokes. When this item is selected, the submenu will display as shown below:

The "Key Repeat Rate" sets the repeat rate when you hold down a key, while the "Key Delay" item sets the delaying time between key repeats

### 1.5.3.8 Power Menu

The Power pull-down menu, as shown below, contains the Power Management settings which help save power

#### Power

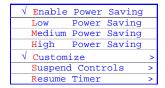

#### @ Enable Power Saving

The "Enable Power Saving" item is the master control for the Power Management features. If this item is disabled, all Power menu items except "Suspend Controls" will be automatically disabled. When this item is selected, no submenu will display. A check mark ( $\sqrt{}$ ) indicates Enabled; an underline (\_) indicates Disabled. The default setting is enabled

#### @ Low Power Saving / Medium Power Saving / High Power Saving / Customize

four items are mutually-exclusive options. You can select one of them. A check mark  $(\sqrt{})$  indicates Enabled; an underline (\_) indicates is enabled an underline (\_) indicates Disabled

### Descriptions of the four options are:

| <u>Options</u>        | <u>Descriptions</u>                                                                                                                                                                                                       |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Max Performance       | Select this option for the pre-defined settings which allow maximum performance but shortest battery life.                                                                                                                |

| Balanced Power Saving | Select this option for the pre-defined settings which allow moderate performance and moderate battery life.                                                                                                               |

| Max Power Saving      | Select this option for the pre-defined settings which allow longest battery life but minimum performance.                                                                                                                 |

| Customize             | Select this option for setting up your own preferences. When this option is selected, the submenu will display as shown below that allows you to set up Power Saving features. (See the next subsection for information.) |

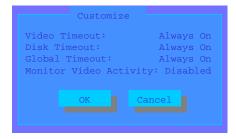

Note: Under Windows98/Windows Me/Windows2000, have built-in ACPI configurations which will override these settings When the "Customize" item is selected, the submenu will display as shown below:

#### **Video Timeout:**

The "Video Timeout" item sets the time-out period for the monitor to power down if it is not in use during the set period. The monitor will power up again when any key is pressed.

The available options are 30 Sec, 2 Min, 5 Min, 10 Min, 15 Min, 30 Min and Always On.

#### **Disk Timeout:**

The "Disk Timeout" item sets the time-out period for the hard disk to power down if it is not in use during the set period. The hard disk will power up again when next accessed.

The available options are 30 Sec, 1 Min, 1.5 Min, 2 Min, and Always On.

#### **Global Timeout:**

The "Global Timeout" item sets the time-out period for initiating Standby mode. Whenever the system. begins idling, the Power Saving starts the time-out for the Standby mode. If the system has been idled for the specified time-out period, system will enter Standby mode.

If Standby mode is in effect, several system subsystems go into standby or off mode so that system power will be reduced. The system will wake up from Standby mode when system activity is detected.

The available options are 1 Min, 2 Min, 4 Min, 6 Min, 8 Min, 12 Min, 16 Min, and Always On.

#### **Monitor Video Activity**

The "Monitor Video Activity" item sets if the video activity will be monitored. If enabled, any activity on the screen (such as showing a movie title) will prevent the monitor from powering down.

The available options are Enabled and Disabled.

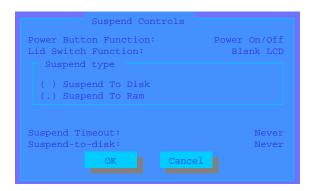

### @ Suspend Controls

The "Suspend Controls" item lets you micromanage several suspend features. When this item is selected, the submenu will display as shown below:

#### **Power Button Function:**

This item sets the function of the power button. The available options are Power On/Off and Suspend/Resume.

Note: When this item is set to "Suspend/Resume", you can turn off the power by pressing the button for 4 seconds.

#### **Lid Switch Function:**

This item sets the sequential event when the top cover is closed while power is on. The available options are Blank LCD, Suspend and CRT/TV Display.

#### **Suspend Type:**

This item sets the suspend mode the system will enter. The available options are Suspend To Disk, Suspend To RAM.

When Suspend-to-RAM mode is initiated, several subsystems will enter standby or power-off mode to conserve power. The system will wake up from Suspend-to-RAM mode when a key is pressed. "Resume Timer", if enabled, can also wake up the system from Suspend-to-RAM mode. When Suspend-to-Disk mode is initiated, the system preserves all the running application programs as a file in a "suspend-to-disk partition" on the hard disk and then turns off automatically.

#### **Suspend Timeout:**

The "Suspend Timeout" item sets the time-out period for initiating suspend mode. This item works in conjunction with previous "Global Timeout" item. When the system enters standby mode, the Power Saving starts the time-out for the Suspend mode. If the system has been in standby mode for the specified time-out period, system will enter Suspend mode.

The Suspend mode is determined by the "Suspend Type" item in the "Suspend Controls" submenu. It can be Suspend-to-RAM, Suspend-to-Disk.

The available options are 1 Min, 5 Min, 10 Min, 20 Min, 20 Min, 30 Min, and Never.

#### Suspend-to-disk:

The "Suspend-to-disk" item sets the time-out period for initiating suspend-to-disk mode. This item works in conjunction with previous "Suspend Timeout" item. When the system enters suspend-to-ram mode, the Power Saving starts the time-out for the Suspend-to-disk mode. If the system has been in suspend-to-ram mode for the specified time-out period, system will enter suspend-to-disk mode.

The available options are 1 Min, 5 Min, 10 Min, 20 Min, 30 Min, and Never.

۷.

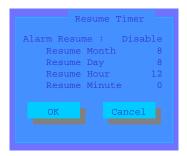

### @ Resume Timer

The Resume Timer" item sets the date and time the system will resume from suspend mode. When this item is selected, the submenu will display as shown below:

The default setting is Disabled

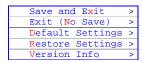

### 1.5.3.9 Exit Menu

The Exit pull-down menu, as shown below, displays ways of exiting SCU. After finished with your settings, you must save and exit SCU so that the settings can take effect

#### Exit

# Descriptions of the Exit choices are:

| <u>Choices</u>   | <u>Descriptions</u>                            |

|------------------|------------------------------------------------|

| Save and Reboot  | Save changes and reboot the system.            |

| Exit (No Save)   | Exit without saving the changes you have made. |

| Default Settings | Load factory default values for all the items. |

| Restore Settings | Restore previous values for all the items.     |

| Version Info     | Show BIOS version information                  |

# 1.5.4 Function Hotkeys

| Fn + F5  | Toggle display output. The display switch sequence, please refer to chapter 6 |

|----------|-------------------------------------------------------------------------------|

| Fn + F6  | Brightness Down (16 levels)                                                   |

| Fn + F7  | Brightness Up (16 levels)                                                     |

| Fn + F10 | Enable/Disable battery warning beep                                           |

| Fn + F11 | Panel on/off                                                                  |

| Fn + F12 | Suspend to RAM or disk                                                        |

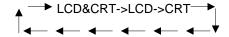

# 1.5.5 Display Out

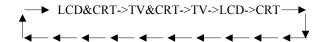

When you boot the system with CRT, display output is LCD&CRT mode.

When boot with CRT, the display switch sequence by hotkey FnF5 is as following:

When boot with CRT and TV, the display switch sequence by hotkey FnF5 is as following:

# 1.5.6 LID

### @ In Non-ACPI Operating System:

LID switch function is dependent on the setting in BIOS setup menu.

"Blank LCD" - LCD will be blank when LID is closed.

| Before LID is closed | LID is closed | LID is opened |

|----------------------|---------------|---------------|

| LCD is active        | LCD is blank  | LCD is active |

| LCD is blank         | LCD is blank  | LCD is blank  |

"Suspend" -system will enter suspend mode when LID is closed.

| Before LID is closed | LID is closed           | LID is opened           |

|----------------------|-------------------------|-------------------------|

| System is On         | System enters Suspend   | System still in Suspend |

| System in Suspend    | System still in Suspend | System still in Suspend |

"CRT/TV Display" -display will be switched to CRT/TV when LID is closed.

When the LID is closed, the LCD will be inactive and external display device will be active.

When the LID is opened, the display devices status (active/inactive) will be restored to the state before the LID is closed.

Some special conditions are list below.

| Before LID is closed    | LID is closed         | LID is opened         |

|-------------------------|-----------------------|-----------------------|

| LCD (active)            | LCD (inactive)        | LCD (active)          |

| CRT (present, inactive) | CRT (active)          | CRT (inactive)        |

| TV(present, inactive)   | TV(inactive)          | TV(inactive)          |

| LCD (inactive)          | LCD (inactive)        | LCD (active)          |

| CRT/TV is present       | CRT/TV is plugged out | CRT/TV is not present |

# @ In ACPI Operating System:

The LID switch function is dependent on the setting of the Power Management in the operating system.

# 1.5.7 VGA Resolution of Windows 98/Me Driver (Need Modifying via VGA Driver)

# LCD(LCD&CRT,TV,TV&CRT)

| Resolution | Color             |

|------------|-------------------|

| 640*480    | 256, 16bit, 32bit |

| 800*600    | 256, 16bit, 32bit |

| 1024*768   | 256, 16bit, 32bit |

# CRT(TV)

| Resolution | Color              |  |

|------------|--------------------|--|

| 640*480    | 256, 16bit, 32bit  |  |

| 800*600    | 256, 16bit, 32bit  |  |

| 1024*768   | 256, 16bit, 32bit  |  |

| 1154*864   | 256, 16bit, 32bit  |  |

| 1280*768   | 256, 16bit, 32bit  |  |

| 1280*1024  | 256, 16bit, 32 bit |  |

| 1600*1200  | 256, 16bit, 32 bit |  |

| 1792*1344  | 256, 16bit         |  |

| 1800*1440  | 256, 16bit         |  |

| 1920*1080  | 256, 16bit         |  |

| 1920*1200  | 256, 16bit         |  |

| 1920*1440  | 256, 16bit         |  |

| 2048*536   | 256, 16bit         |  |

### 1.5.8 LED Indicators

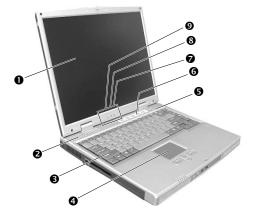

System has nine status LED indicators to display system activity which include below LCD panel unit and above keyboard:

### 1.5.8.1 Three LED indicators below LCD panel unit:

From left to right that indicate AC POWER, BATTERY POWER and BATTERY STATUS

- AC POWER: This LED lights green when the notebook is being powered by AC, and flash (on 1 second, off 1 second) when Suspend to DRAM is active using AC power. The LED is off when the notebook is off or powered by batteries, or when Suspend to Disk.

- ® BATTERY POWER: This LED lights green when the notebook is being powered by batteries, and flashes (on 1 second, off 1 second) when Suspend to DRAM is active using battery power. The LED is off when the notebook is off or powered by AC, or when Suspend to Disk.

- ® BATTERY STATUS:During normal operation, this LED stays off as long as the battery is charged. When the battery charge drops to 10% of capacity, the LED lights red, flashes per 1 second and beeps per 2 second. When AC is connected, this indicator glows green if the battery pack is fully charged, or orange (amber) if the battery is being charged.

### 1.5.8.2 Five LED indicators in front of palm rest:

From left to right that indicates CD-ROM/MO, HARD DISK DRIVE, , NUM LOCK, CAPS LOCK and SCROLL LOCK.

### 1.5.9 Power Management

### **1.5.9.1 Features**

- ® APM 1.2/1.1/1.0 compliant

- ® Battery warning beep

- ® Battery low suspend to RAM/disk

- ® Cover switch close to panel off, standby, or suspend

- ® Hot-key suspend

- ® Hot-key panel on/off

- ® Auto clock throttling to prevent overheating

- ® ACPI 1.0 compliant

- ® User programmable standby/suspend timers and sustained events when OS doesn't support APM/ACPI

### 1.5.9.2 Device power state

Note: Each device power states are described in the chapter titled Components & Drives. Please refer to those paragraphs. BIOS will not automatically manage devices' power states if ACPI engaged or APM engaged but disabled.

### 1.5.9.3 System power state

### Definitions when ACPI engaged

### **Global States:**

- G0 Global system is working

- G1 Global system is sleeping

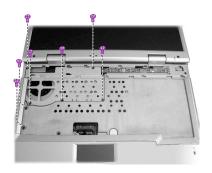

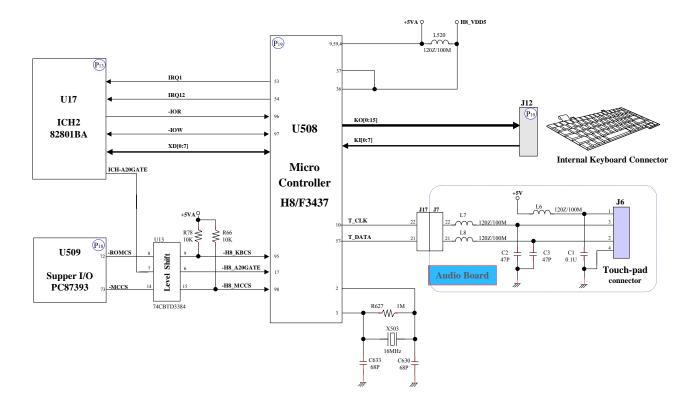

- G3 Global system is mechanical-off