| 0. Introduction                               | P. 2  |

|-----------------------------------------------|-------|

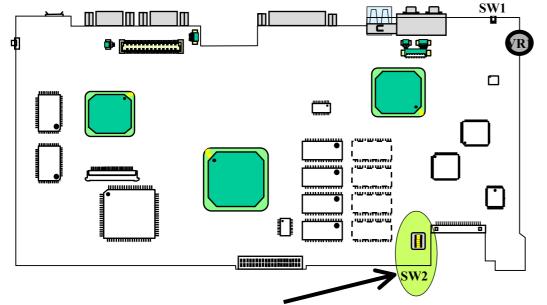

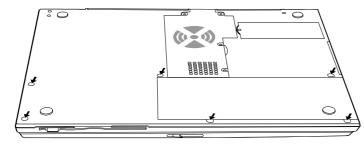

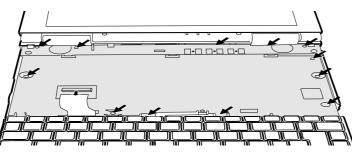

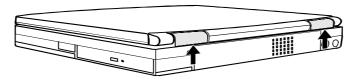

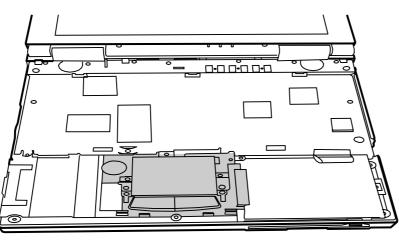

| 1. Definition & Location Connectors/ Switches | P.20  |

| 2. Definition & Location Major Components     | P.21  |

| 3. Pin Descriptions of Major Components       | P.24  |

| 4. Switch Setting                             | P.51  |

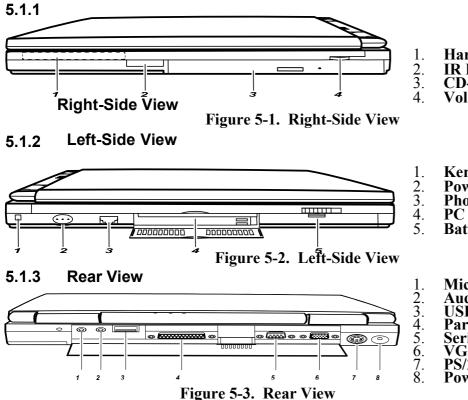

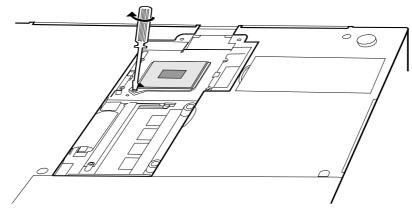

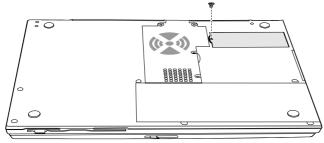

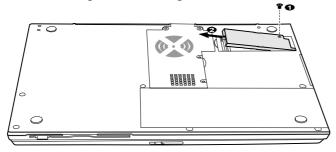

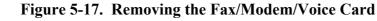

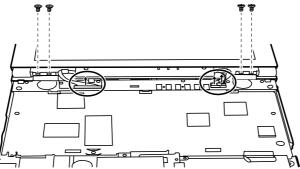

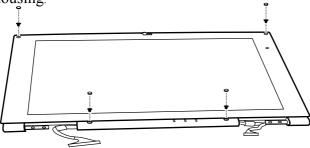

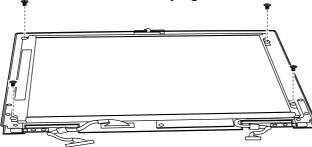

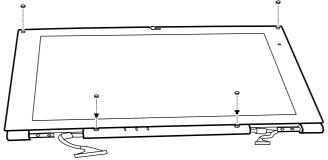

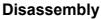

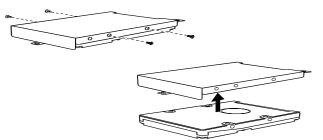

| 5. Assembly & Disassembly                     | P.52  |

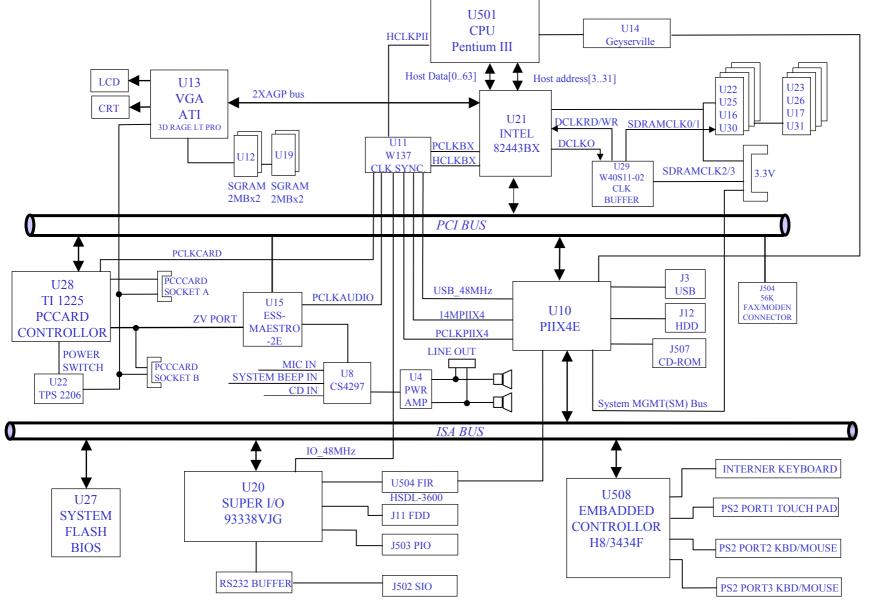

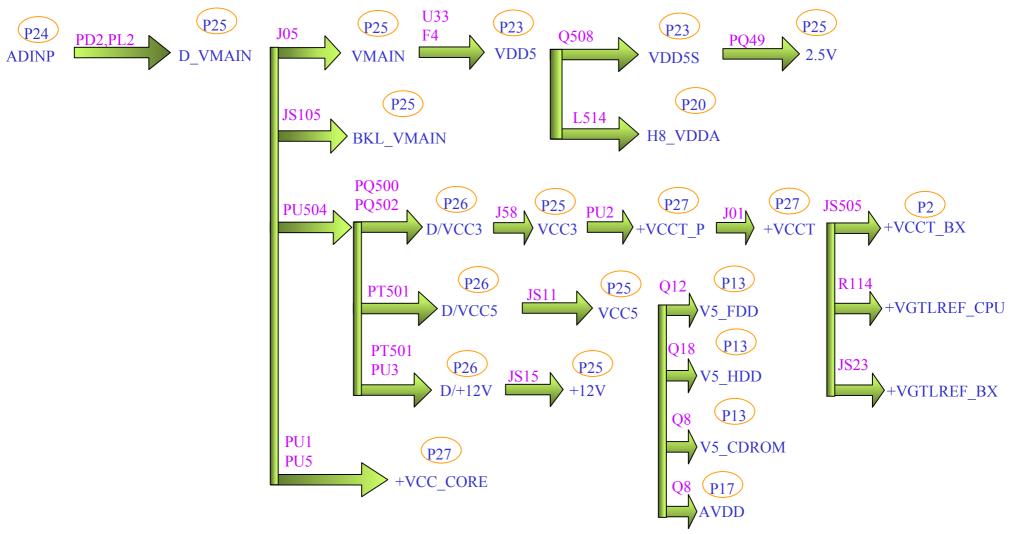

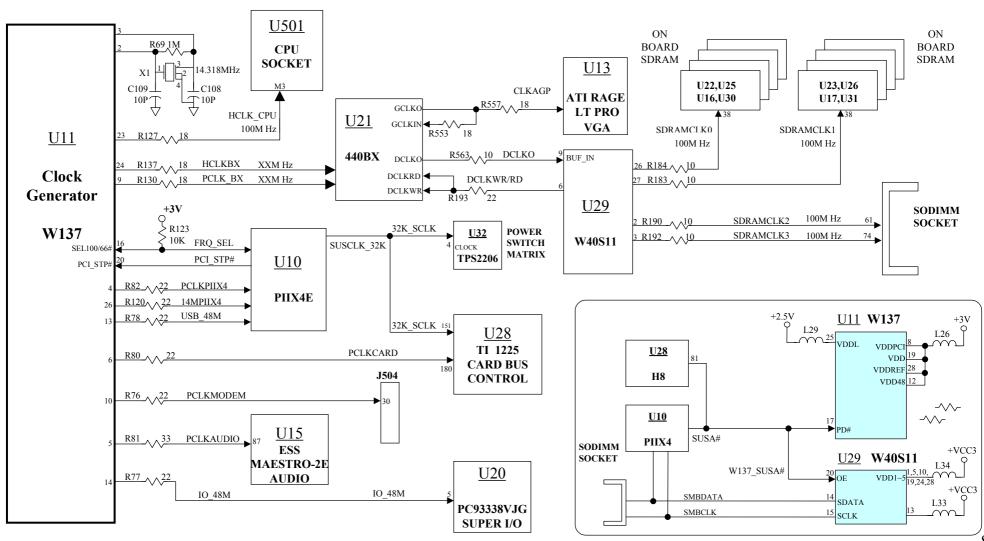

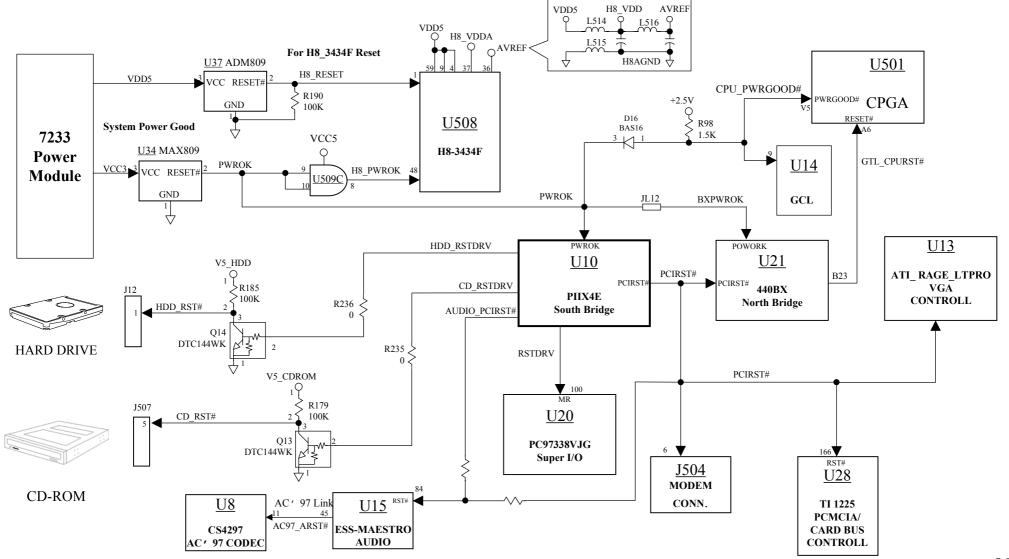

| 6. 7233 Block Diagram                         | P.74  |

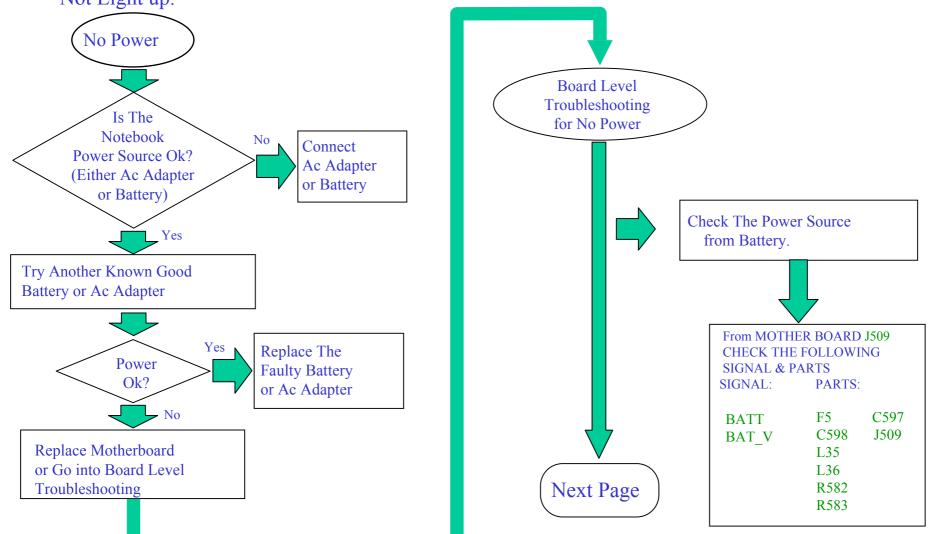

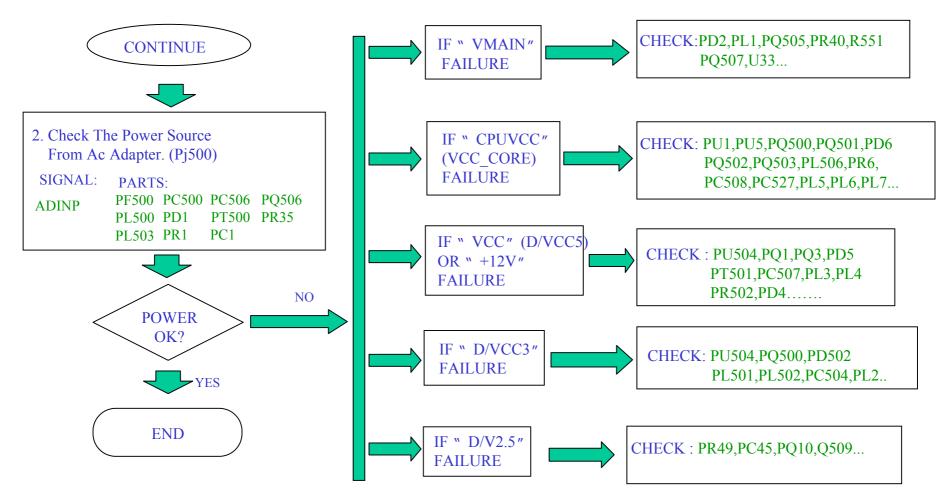

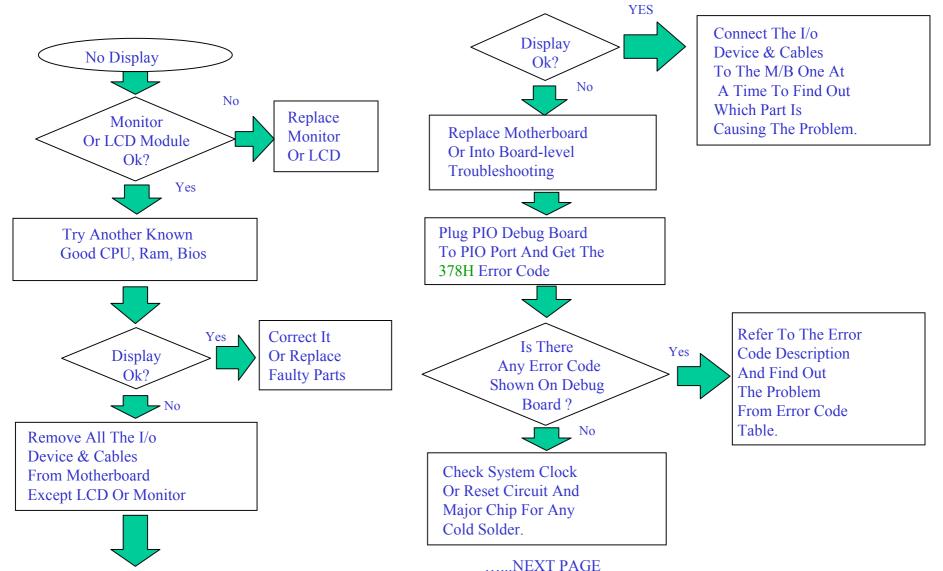

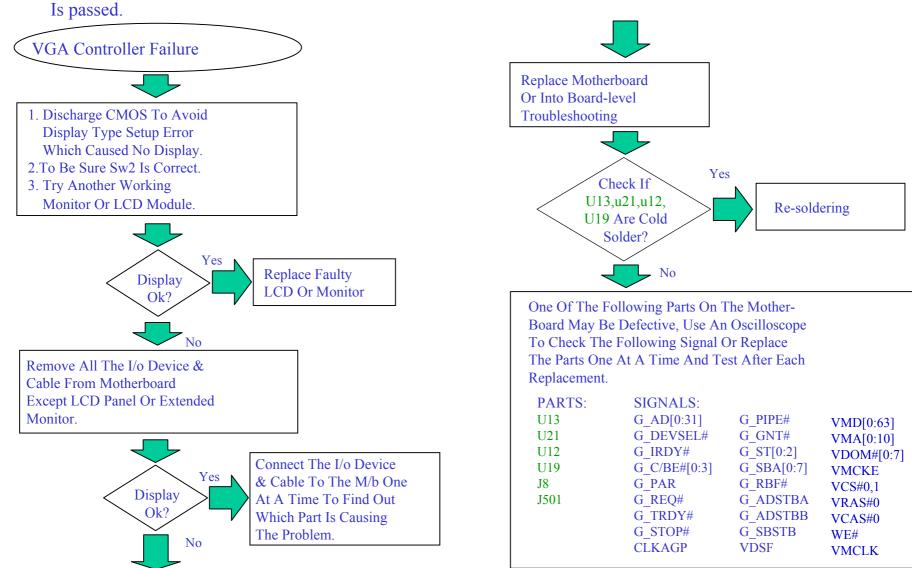

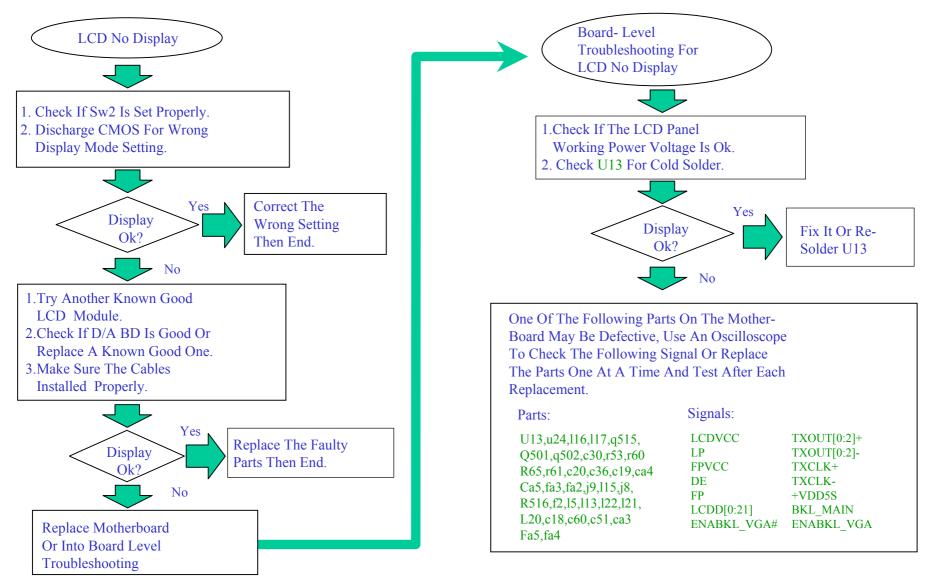

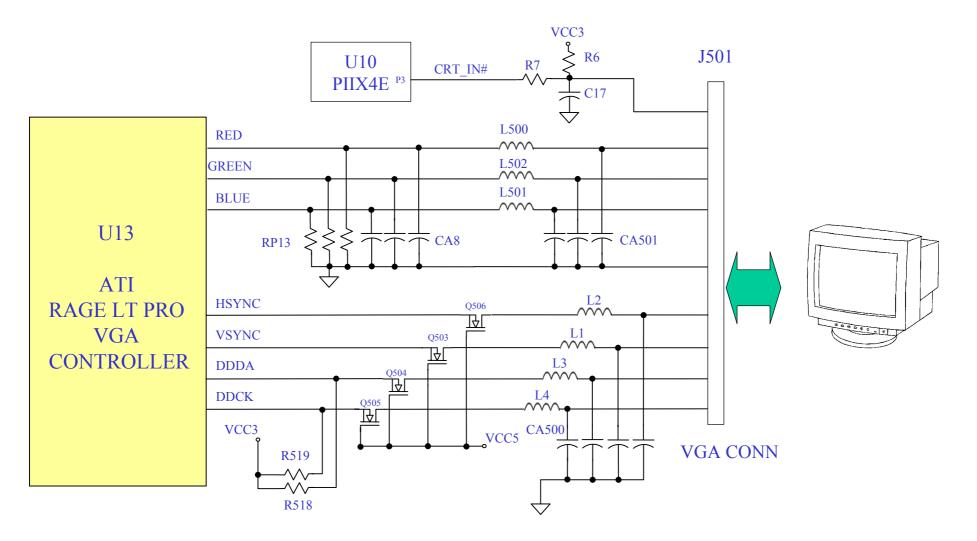

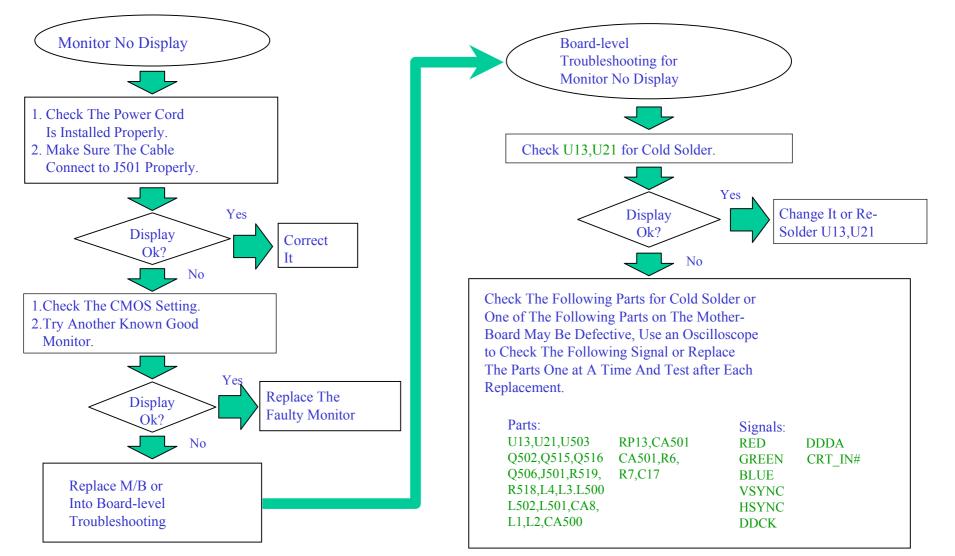

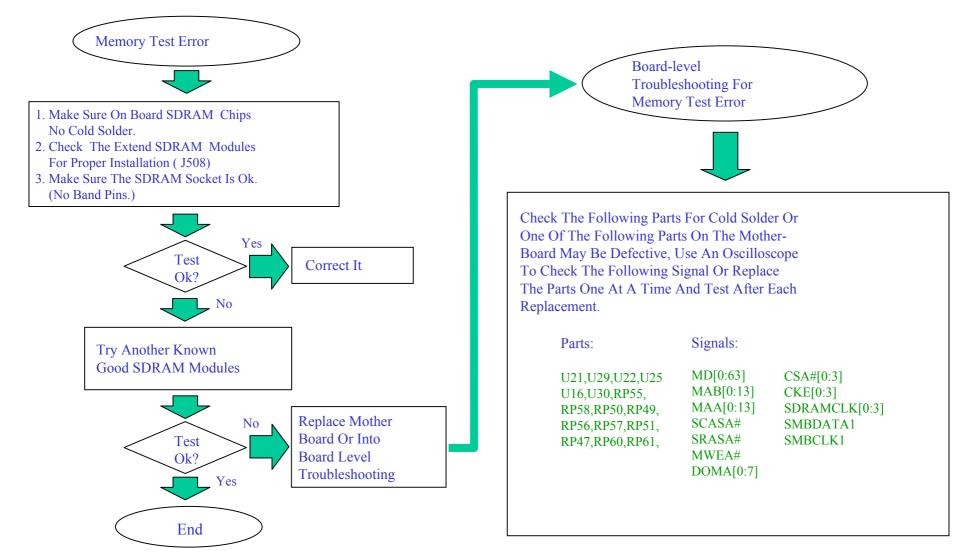

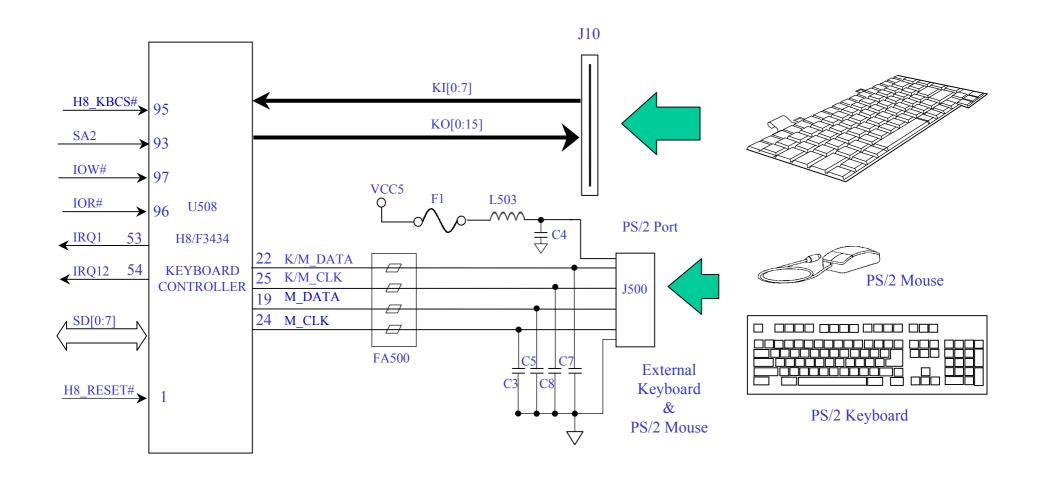

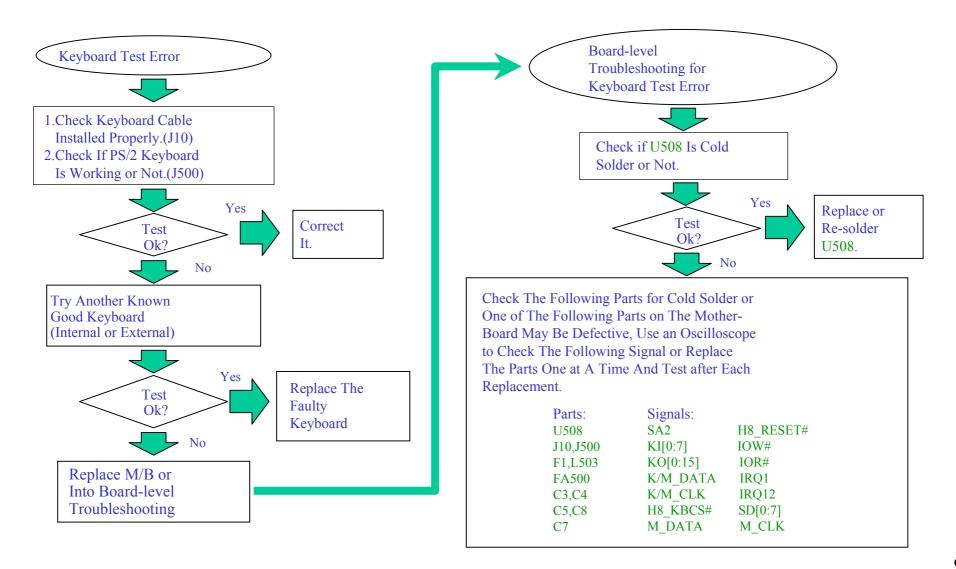

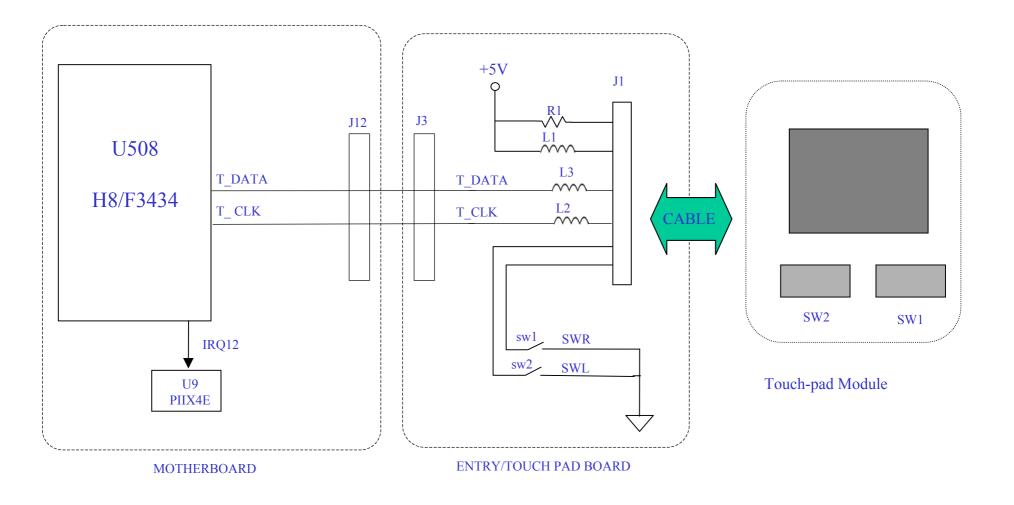

| 7. Maintenance Diagnostics                    | P.75  |

| 8. Trouble Shooting                           | P.78  |

| 9. Spare Parts List                           | P.112 |

| 10. Circuit Diagram                           | P.122 |

1

## **0** Introduction

### 0.1 General Description

This document describes the engineering specification for 7233 portable notebook computer system.

### 0.2 System Overview

This system is based on PCI architecture and is fully compatible with IBM PC/AT specification, which have standard hardware peripheral interface and support Intel Pentium family. The power management complies with Advanced Configuration and Power Interface (ACPI) 1.0. It also provides easy configuration through CMOS setup which is built in system BIOS software and can be pop-up by pressing F2 at system start up or warm reset. System also provides icon LEDs to display system status, such as AC Power indicator, FDD, HDD, NUM LOCK, CAP LOCK, SCROLL LOCK, SUSPEND MODE and battery present, capacity & charging status. It also equipped with Zoom Video capture port, FIR, USB port, 3D stereo audio functions.

The 7233 model motherboard will accept Intel Mobile Pentium III / Celeron processors in uPGA2 package operating at 450/500 MHz (Intel Pentium III processor w/o Geyserville technology)and 600/650/700 MHz (Intel Pentium III processor w/ Geyserville technology),450/500/550 MHz(Intel Celeron processor) with a system bus speed of 100 MHz. The integrated L2 cache is designed to help improve performance, it complement the system bus by providing critical data faster and reducing total system power consumption.

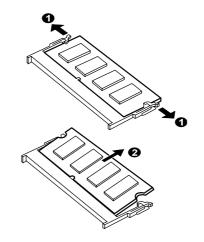

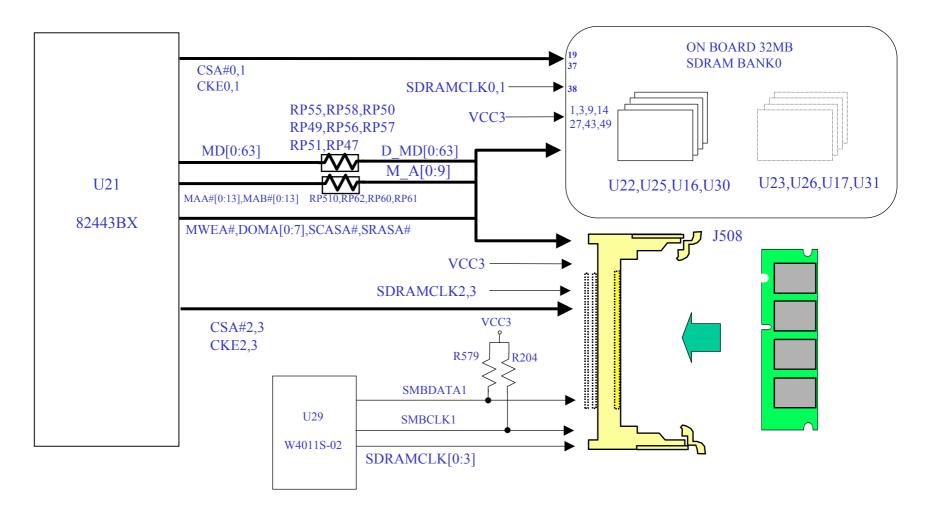

The memory subsystem supports 32MB SDRAM on board and one 144-pin SDRAM SO-DIMM module for upgrading up to 128 MB.

The Intel 440BX AGPset brings third important firsts to the mobile PC environment: (1) Concurrent PCI (PCI 2.1) reduces CPU latencies for smoother video and more realistic audio; (2) Universal Serial Bus (USB) technology makes Plug and Play peripheral connections a reality.(3)Accelerated Graphics Port (AGPSpecification, Rev 1.0 (4/12/96) support up to 2X. The Intel 440BX AGPset also contains an integrated PCI Bus Mastering IDE controller with two high performance IDE interfaces and supports Ultra 33 " synchronous DMA mode which transfers up to 33 Mbytes per second. In addition, the 440BX AGPset supports Intel's new Dynamic Power Management Architecture (DPMA) for consuming less power consumption than earlier PCIset designs and supports Advanced Configuration and Power Interface (ACPI) 1.0 for longer battery life in mobile systems.

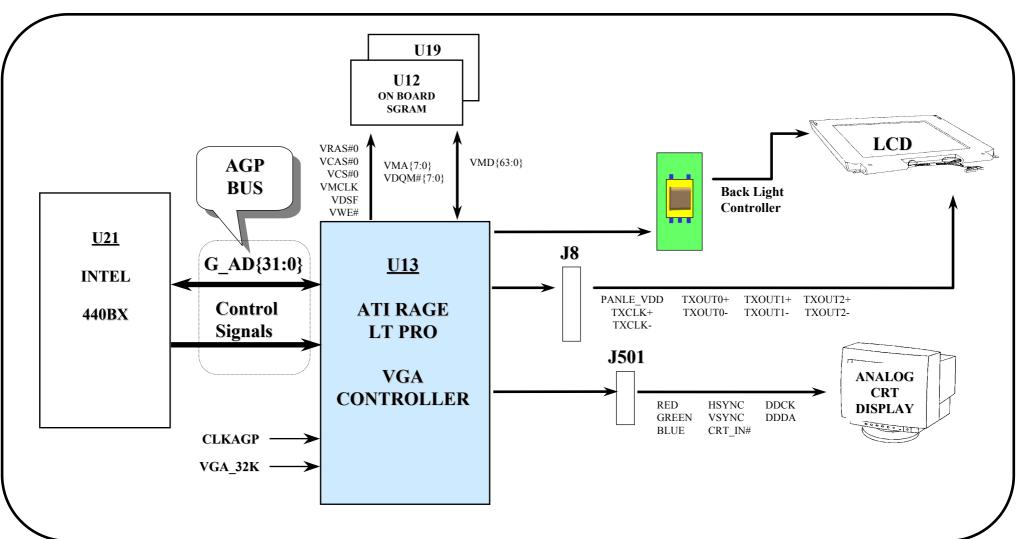

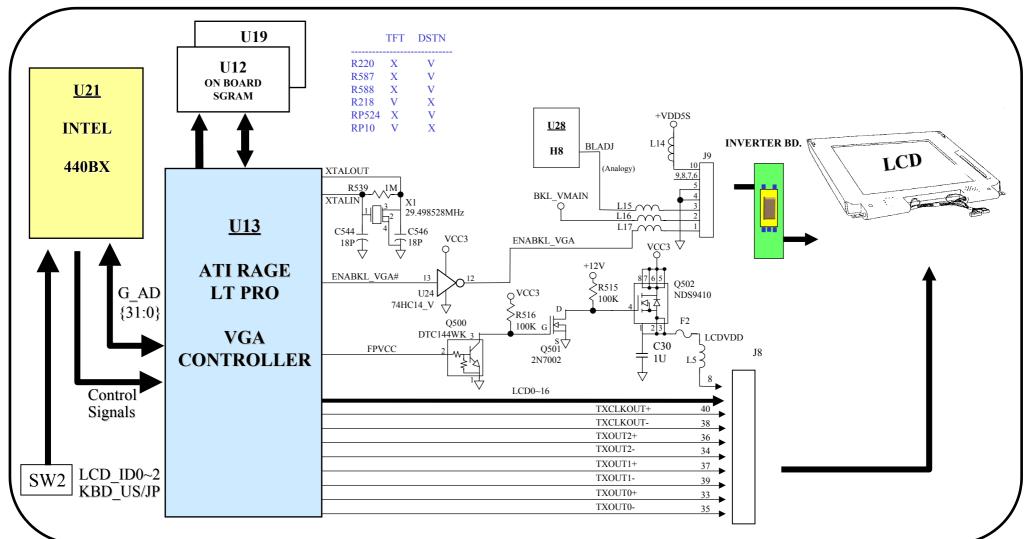

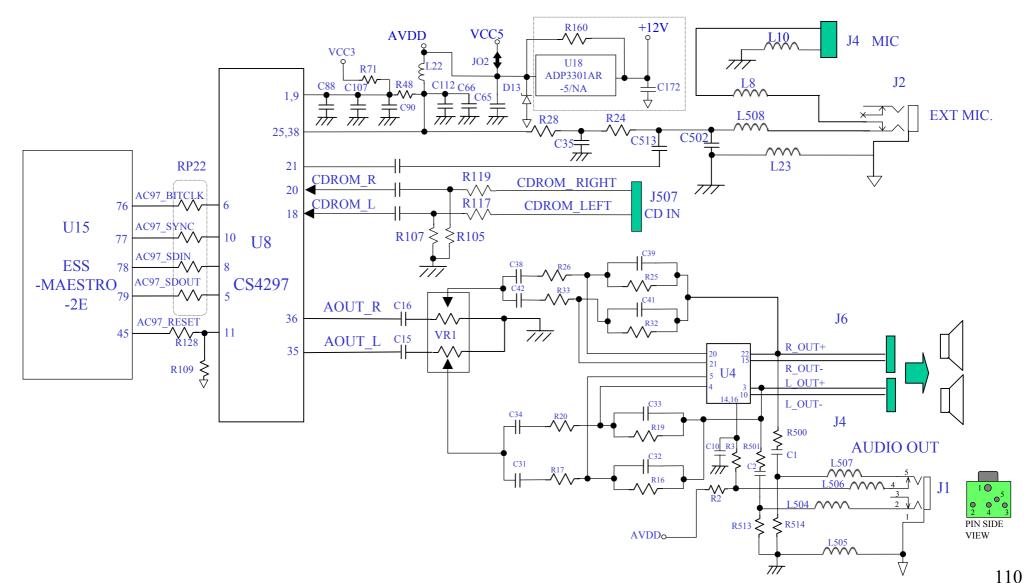

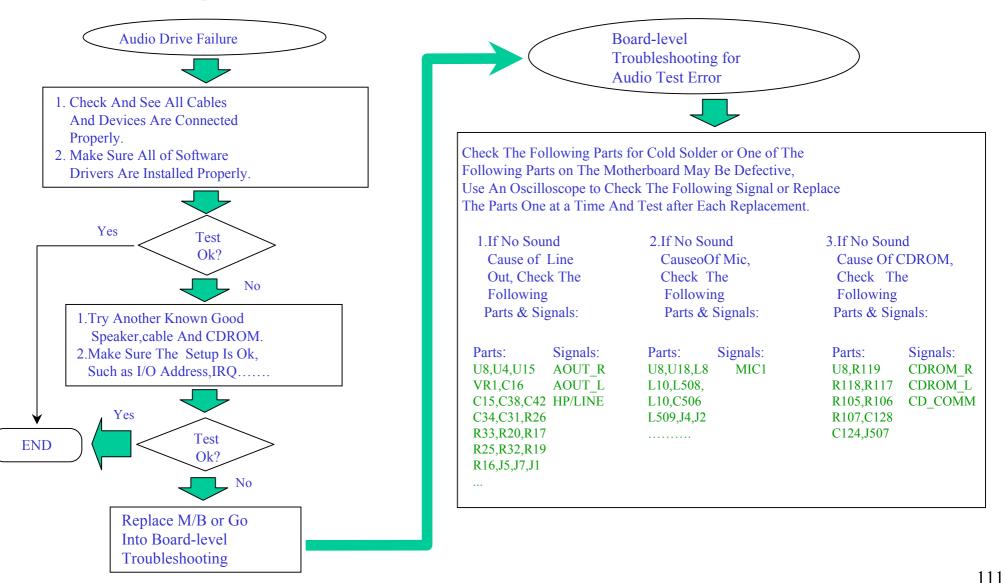

The ATI 3D RAGE LT PRO VGA controller provides LCD,CRT and supports 2D and 3D acceleration ,ZV port,66MHz SGRAM,DVD, ACPI power management ,integrated LVDS...etc. The TI 1225 cardbus controller supports PCMCIA and CARDBUS. The National Semiconductor PC97338 Super I/O controller integrates the standard PC I/O functions: floppy interface, two FIFO serial ports, one EPP/ECP capable parallel port, and support for an IrDA 1.1, 1.0 and sharp ASK compatible infrared interface. To provide for the increasing number of multimedia applications, an

Maestro-2 audio controller and the CODEC CS4297 is integrated onto the motherboard both. The Maestro-2 provides 16-bit stereo, Sound Blaster Pro and Windows Sound System compatibility and full-duplex capabilities to meet the demands of interactive multimedia applications

A full set of software drivers and utilities are available to allow advanced operating systems such as Windows 95 or Windows 98 to take full advantage of the hardware capabilities. Features such as bus mastering IDE, Windows 95-ready Plug N · Play, Advanced Power Management (APM) with application restart, software-controlled power shutdown.

Following chapters will have more detail description for each individual sub-systems and functions

### Hardware System

### 0.3 System parts

- Central ProcessingJnit : Intel Mobile Pentium III / Celeron microproceessor in uPGA2 package .

- Intel 440BX AGPset Host bridge with DRAM controller

- PIIX4M: PCI/ISA bridge with IDE/USB/PMU controller

- Video ControllerATi 3D Rage LT Pro 328-pin BGA

- Super I/O Controller: NS PC97338VJG

- PCMCIA Interface Controller: TI 1225

- Keyboard System: H8(3434) UNIVERSAL KEYBOARD CONTROLLER

- 3D Audio System: EES Maestro-2 PQFP100 AND CODEC CS4297 FIR port: HP HSDL-3600#007 FIR module

- FAX/MODEM:ASKEY 56Kbps Fax Modem , Software Modem

### **0.4 CPU**

The Intel Mobile Pentium III processor will be offered at 450 MHz, 500 MHz with a system bus speed of 100 MHz. The 500 MHz processor will also be offered at a later date to run at higher frequency (600 MHz and 650 MHz) usingGeyserville technology, which enables the CPU to switch bus ratios and core speeds without being reset. The MobilCeleron processor is the first mobile processor with an integrated L2 cache among thCeleron processors. The MobilCeleron processor will initially be offered at 450 MHz, 500 MHz and 550 MHz with a system bus speed of 100 MHz. It consists of a Mobile Pentium III/Celeron processor with an integrated L2 cache and a 64-bit high performance system bus. The integrated L2 cache is designed to help improve performance, it complements the system bus by providing critical data faster and reducing total system power consumption. The Mobile Pentium(Heron processor 64-bit wide Low Power Gunning Transceiver Logic (GTL+) system bus is compatible with the 440(BXPSet, and provides a glue-less, point-to-point interface for an I/O bridge/memory controller.

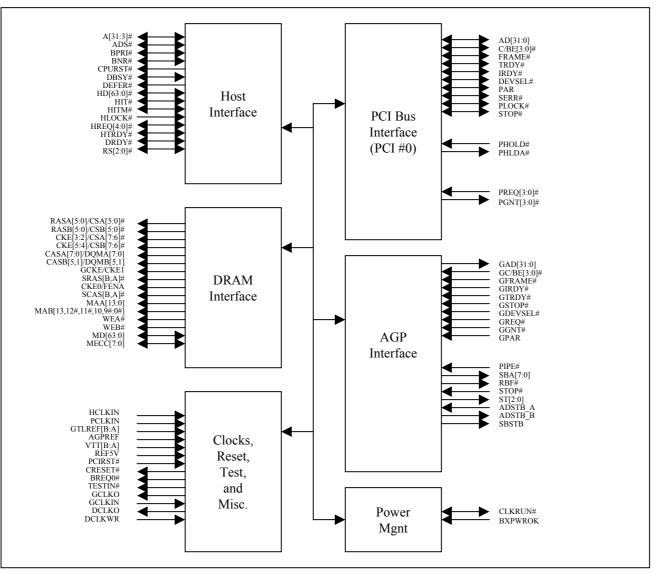

### 0.5 Intel 440BX AGPset

### 0.5.1 Intel 440BX AGPset Host Bridge

- Support Full Symmetric Multiprocessor Protocol for up to two processors

- 64-bit GTL+ based Host Bus Interface

- 32-bit Host address Support

- 64-bit Main Memory Interface with optimized support for SDRAM at 100 and 66/60 MHz

- 32-bit Primary PCI Bus Interface (PCI0) with integrated PCI arbiter

- AGP Interface (PCI1/AGP) with 133 MHz data transfer capability configurable as a Secondary PCI Bus

- Extensive Data Buffering between all interfaces for high throughput and concurrent operations

- Processor/host bus support

- Optimized for Pentium II processor at 100 MHz host bus frequency; Support for 66 MHz

- **—** In-order transaction and dynamic deferred transaction support

- Desktop optimized GTL+ bus driver technology (gated GTL+ receivers for reduced power)

- Integrated DRAM controller

- 8 to 256Mbvtes

- Supports up to 4 double-sided DIMMs (8 rows memory)

- Get-bit data interface with ECC support (SDRAM only)

- Standard and Registered SDRAM (Synchronous) DRAM Support (x-1- 1-1 access @ 66 MHz , x-1-1-1 access @ 100MHz)

- Enhanced SDRAM Open Page Architecture Support for 16- and 64-Mbit

- DRAM devices with 2k, 4k and 8k page sizes

- PCI bus interface

- PCI Rev. 2.1, 5V, 33MHz interface compliant

- **\_\_\_\_ PCI Parity Generation Support**

- Data streaming support from PCI to DRAM

- Delayed Transaction support for PCI-DRAM Reads

- Supports concurrent CPU, AGP and PCI transactions to main memory

- AGP interface

- Supports single AGP compliant device (AGP-66/133 3.3V device)

- **\_\_\_\_** AGP Specification Rev 1.0 compliant

- **\_\_\_\_** AGP-data/transaction flow optimized arbitration mechanism

- AGP side-band interface for efficient request pipelining without interfering with the data streams

- AGP-specific data buffering

- Supports concurrent CPU, AGP and PCI transactions to main memory

- AGP high-priority transactions (" expedite" )support

- Power Management Functions

- Stop Clock Grant and Halt special cycle translation (host to PCI Bus)

- Dynamic power down of idle DRAM rows

- \_ Independent, internal dynamic clock gating reduces average power dissipation

- Packaging/Voltage

- \_\_\_\_\_ 492 Pin BGA

- **\_\_\_\_\_\_ 3.3V core and mixed 5V,3.3V and GTL I/O**

- Supporting I/O Bridge

- System Management Bus (SMB) with support for DIMM Serial Presence Detect (SPD)

- PCI-ISA Bridge (PIIX4E)

- 3.3V core and mixed 5V, 3.3V I/O and interface to the 2.5V CPU signals via open-drain output buffers

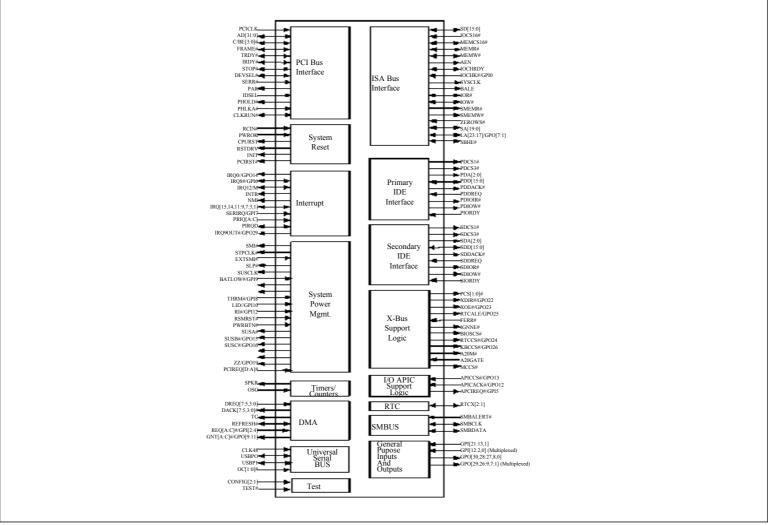

### 0.5.2 Intel PIIX4M (82371MB)

- Supported Kits for both Pentium and Pentium II Microprocessors

- 82430TX ISA Kit

- 82440LX ISA/DP Kit

- Multifunction PCI to ISA Bridge

- Supports PCI at 30 MHz and 33 MHz

- **Supports PCI Rev 2.1 Specification** \_\_\_\_

- Supports Full ISA or Extended I/O (EIO) Bus

- Supports full Positive Decode or Subtractive Decode of PCI

- Supports ISA/EIO at 1/4 of PCI Frequency

- .

- **Ultra-Low Power for Mobile Environments**

- Power-On Suspend and Soft-OFF for Desktop Environment

- All Registers Readable/Restorable for Proper Resume From 0.V Suspend

- Power Management Logic .

- Global and Local Device Management

- Suspend and Resume Logic

- Supports Thermal Alarm

- Support for External Microcontroller \_\_\_\_

- Full Support for Advanced Configuration and Power Interface (ACPI)

- **Revision 1.0 Specification and OS Directed Power Management**

- **Integrated IDE Controller**

- **Independent Timing of Up to 4 Drives**

- PIO Mode 4 Transfers Up to 14 Mbytes/sec

- Supports " Ultra DMA/33" Synchronous DMA Mode Transfers Up to 33 \_\_\_\_ Mbvtes/sec

- Integrated 16 x 32-Bit Buffer for IDE PCI Burst Transfers

- Supports Glue-Less " Swap-Bay" Option With Full Electrical Isolation

- **Enhanced DMA Controller**

- Two 82C37 DMA Controllers

- Supports PCI DMA With 3 PC/PCI Channels and Distributed DMA Protocols (Simultaneously)

- Fast Type-F DMA for Reduced PCI Bus Usage

- Interrupt Controller Based on Two 82C59 •

- 15 Interrupt Support Independently Programmable for Edge/Level Sensitivity

- Supports Optional I/O APIC

- Serial Interrupt Input

- . Timers based on 82C54

- System Timer, Refresh Request, Speaker Tone Output

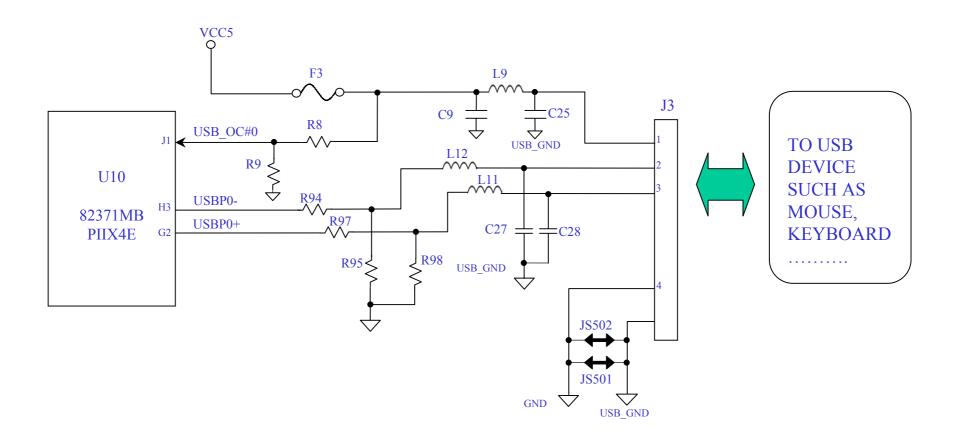

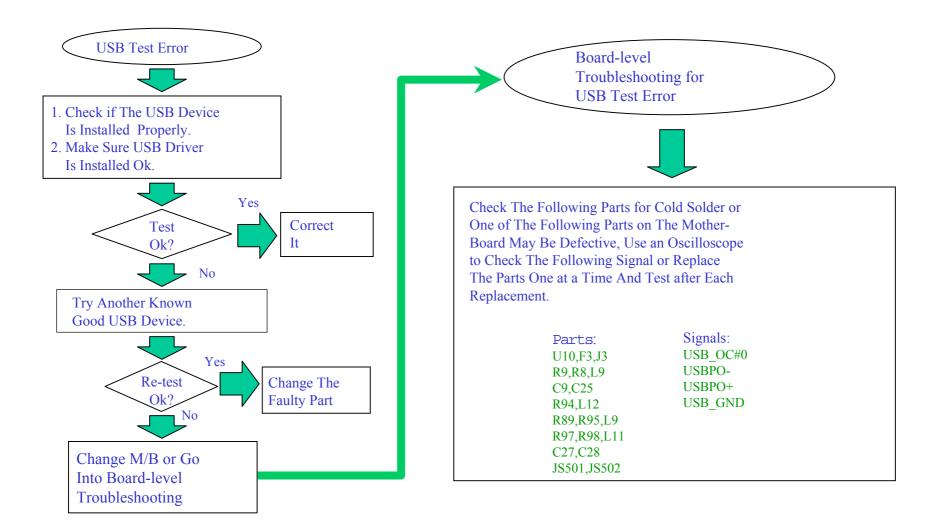

- USB

- Two USB 1.0 Ports for Serial Transfers at 12 or 1.5 Mbit/sec

- Supports Legacy Keyboard and Mouse Software With USB-Based Keyboard

- and Mouse Supports UHCI Design Guide Revision 1.1 Interface

- **SMBus** .

- Host interface Allows CPU to Communicate via SMBus

- Slave Interface Allows External SMBus Master to Control Resume Events

- **Real-Time Clock** .

- 256-Byte Battery-Back CMOS SRAM

- Includes Date Alarm

- **Two 8-Byte Lockout Ranges**

- **Microsoft Windows\* 95 Compliant**

- 324 mBGA Package

#### 0.6 VGA Controller: ATI 3D RAGE LT PRO

- Supports AGP 1X and AGP 2X (133 MHz) Supports AGP' s pipelined sideband protocol. Support dual CRT controller

- Dual independent displays (LCD/CRT, CD/TV, CRT/TV). Second triple-DAC for TV allows displays likes CRT+TV/LCD, \_\_\_\_

- LCD+TV/CRT, LCD+CRT/TV and the resolutions, refresh rates and display

- data can be completely independent.

- **Primary display path supports:** •

- VGA and accelerated modes

- Video overlav

- Hardware cursor and hardware icon \_\_\_\_

- Palette gamma correction.

- Supports both independent displays at 1024 x 768, 24bpp, 75Hz (see mode tables for details).

- Secondary display path supports:

- Accelerated modes

- YUV422 video data \_\_\_\_

- 24-bit palette

- Video genlocking supported for both CRTCs.

- Integrated dual 65MHz LVDS interface

- Up to 10 LVDS channels for power and EMI reduction.

- Dual pixel SXGA resolution TFT panels \_\_\_\_

- XGA resolution DSTN panels. \_\_\_\_

- 24bpp TFT (SGA/XGA) using dual pixel LVDS (versus 18 bpp using direct

- digital interface). 455 Mbps/channel with 65 MHz pixel clock rate.

- DSTN-120Hz XGA (1024 x 768 60Hz) and 170 Hz SVGA (800 x 600 85Hz) \_\_\_\_\_

- 3 pairs (+1 clock ) and 4 pairs (+1 clock ) modes for both single and dual pixel \_\_\_\_ LVDS.

- **FPDI-2** compliant; compatible with receivers from National Semiconductor, Texas Instruments, and THine.

- LVDS eye pattern to improve testability of LVDS module.

- Flat panel power management: •

- Automatic power down panel by programmable internal timer

- Standby/Suspend pins for hardware Power Management support. \_\_\_\_

- Standby/Suspend registers for software Power Management support.

- Flat panel support:

- Color STN/DSTN/CSTN LCD panels up to XGA (1024 x 768) resolution, up to 16MHz refresh rate, up to 256k colors on an 8-color panel. Color TFT panel up to 1600 x 1280 resolution, up to 24-bit per pixel,

- single/double pixel per clock.

- 2/4 levels of frame modulation can be done on 9-bit, 12-bit and 18-bit TFT panels.

- Hardware Z-buffer support with both DSTN and TFT panels.

- Integrated LVDS interface support.

- Support for Panel Link Interface.

- Support external Panel Link transmitter. Panel ID to allow multiple panel support without swapping BIOS. \_\_\_\_

- Five bits allocated for panel ID. \_\_\_\_

- DDC support for LCD monitors. \_\_\_\_

- General purpose I/O pins available to support DDC on LCD monitor

applications.

- Integrated a floating-point set-up engine

- processing up to 1.2 million triangles per send.

- Supports 66 MHz SGRAM:

- 64-bit, 66MHz SGRAM interface

- 800 MB/s of low-latency frame buffer bandwidth

- ZV Port (PCMCIA compliant with CCIR601 timing)

- Allows transfer of video data directly into frame buffer without loading down PCI bus.

- Dedicated video port guarantees video frame rates (30 frames per second)

- Maximum 40 MHz, 16bpp YUV422 (PCMCIA specs 16 MHz maximum)

- **DVD and Video Support**

- Enhanced motion compensation acceleration

- 4-tap horizontal and 2-tap vertical high quality DVD video scaler.

- De-interlacing filter, Video on graphics overlay, Multi-stream video

- Color-space conversion, Scatter-gather bus-master, Planar YUV mode

- ATI Multimedia Channel (AMC) video input port

- Zoom Video input port (ZV-port) NTSC and PAL TV- out

- Improves software DVD/MPEG-2 frame rate by 20 to 30%.

- Provides full motion MPEG-2 playback on Pentium II processors

- An integrated TV encoder with on-chip triple –DAC allows simultaneous CRT/LCD/TV output with these outstanding TV-out characteristics:

- Support for Microvision 7.01 copy protection standard (required by DVD) plavers)

- YUV Direct/Passthrough mode for video/MPEG playback

- DVD provides the best quality for movie playback

- Secondary Display support for RGB modes as well as full screen YUV mode.

- 1024 x 768 24bpp support

- Line 21 Closed Caption and Extended Data Service support for encoding in Vertical Blanking Interval (VBI) of TV signal. CGMS-A DVD copy management support in VBI through Line-20 and/or

- Extended Data Service (Line-21 Field 2).

- UV filtering for a higher quality picture and reduced flicker.

- TV-out power management support. \_\_\_\_

- Proven Y flicker filter with programmable (2,3,4,5,6)taps.

- Eliminates " Composite Dot Crawl" problem for both NTSC and PAL.

- Varied TV-OUT output formats:

- **\_\_\_** NTŚĆ.

- PAL B, D, G, H, I (PAL B, D, G, H, I are the same for TV-OUT), M(Brazil), N (Uruguay, Paraguay), CN (Argentina). Composite Video (available on the majority of TV ' s).

- S-Video(available on Mid to High End TV<sup>7</sup> s, less colour artifacts, better resolution).

- SCART-RGB connector (direct RGB into the TV-high quality resolution).

- Output signal is generated at 50+Msamples/sec to virtually eliminate the need for external analogue filtering.

- Signal is digitally filtered to insure that it does not exceed bandwidth specifications of TV standards, this insures that it can be recorded, can be broadcast, and will comply with FCC regulations when input into poorly shielded TV sets.

- Can detect whether TV/VCR is connected or not (Power-down/Power-up over-ride via software).

- **Supports 3D Acceleration**

- integrated 1 million triangle/s set-up engine

- 4K on-chip texture cache.

- Full screen or window double buffering for smooth animation \_\_\_\_

- Hidden surface removal using 16-bit Z-buffering \_

- \_\_\_\_

- \_\_\_\_

- Edge anti-aliasing Sub-pixel and sub-texel accuracy Gouraud and specular shaded polygons

- Forspectively correct mip-mapped texturing with chroma-key support. Full support of Direct3D texture lighting. \_\_\_\_

- Extensive 3D mode support: Draw in RGBA32,RGBA16, and RGB16.

- Texture map modes: RGBA32,RGBA16,RGB8,ARGB4444, YUV444. Compressed texture mode: YUV422, CLUT4 (Cl4), CLUT8(Cl8), VQ

- Mobile AGP 1.0 and mobile PCI 1.0 support.

- Pin, Register and Timer modes for hardware and software power management.

- Panel bias voltage and digital power control. Self-refresh(EDO,SGRAM), and CBR refresh (EDO) in Suspend mode using external 32 KHz source (F32KHz pin). Enhanced line buffer allows vertical filtering of native MPEG-2 size (720 x 480) images. DVD/MPEG-2 decode assist provides dramatically improved frame rate Hardware mirroring for flipping video images in video images in video conferencing

- systems.

- Smooth video scaling and enhanced YUV to RGB color space conversion

- Front and back end scalers support multi-stream video for video conferencing

- Filtered horizontal/vertical, up/down, scaling enhances playback quality.

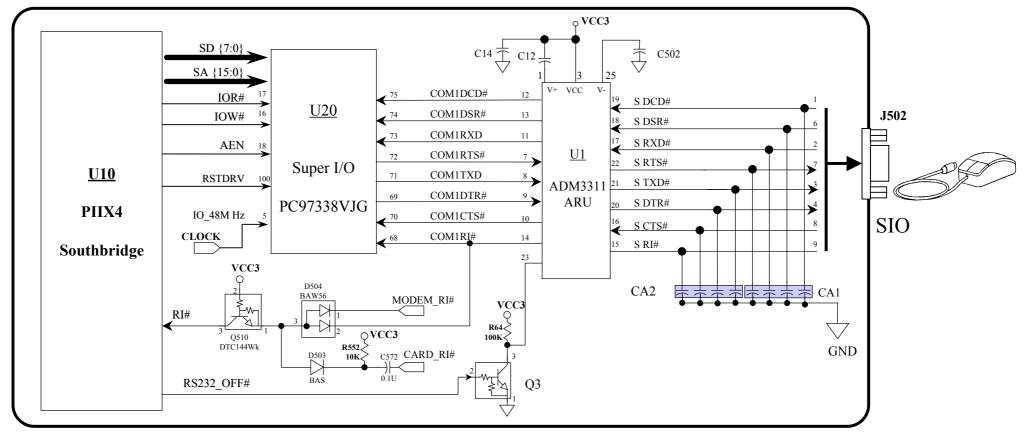

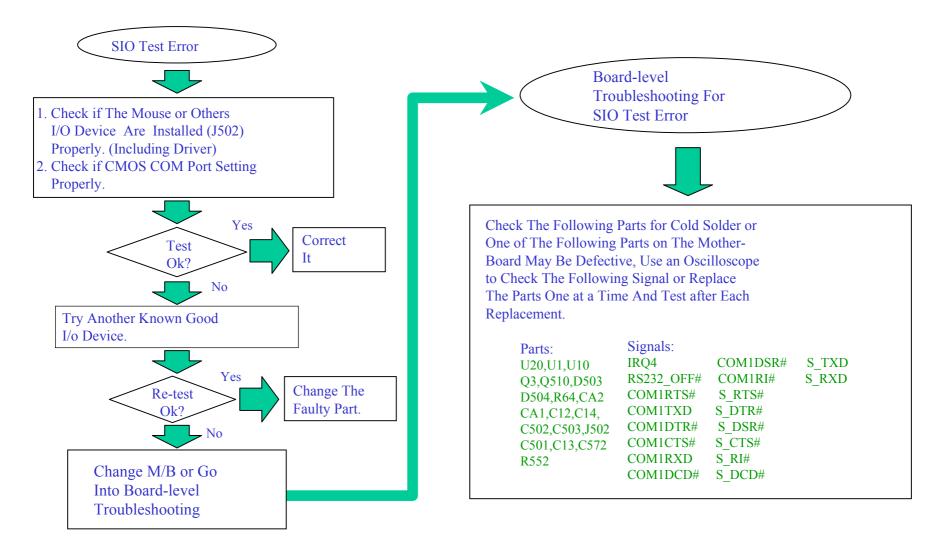

#### 0.7 Super IO: NS PC 97338VJG

The PC97338 is a fully ACPI 1.0 and PC97 compliant, ISA based Super I/O. It is functionally compatible with the PC87338. It includes a Floppy Disk Controller (FDC), two Serial Communication Controllers (SCC) for UART and Infrared support, one IEEE1284 compatible Parallel Port, and two general purpose Chip signals for game port support. The device ports power management as well as 3.3V and 5Voperation making it particularly suitable for notebook and sub-notebook applications. The PC87338 and PC97338 are fully compliant to the Plug and Play specifications included in the ware Design Guide for Microsoft Windows 95".

- Meets ACPI 1.0 and PC97 requirements Backward compatible with PC87338 100% compatibility with Plug and Play requirements specified in the Hardware Design Guide for Microsoft Windows 95" ISA, EISA, and Micro-mixed Channel architectures A special Plug and Play module includes: \_\_\_\_\_\_\_\_ Flexible IRQs, DMAs and base addresses \_\_\_\_\_\_\_\_ Flexible IRQs, DMAs and base addresses

- - General Interrupt Requests (IRQs) that can be multiplexed to the ten Supported IRQs A new, high performance, on-chip Floppy Disk Controller (FDC) provides: Software compatibility with the PC8477, which contains a superset of the floppy

- - disk controller functions in the  $\mu$  DP8473, the NEC  $\mu$  PD765A and the N82077 A modifiable 13-bit address

- Ten IRQ channel options Four 8-bit DMA channel options

- 16-byte FIFO

- Burst and non-burst modes

- Low-power CMOS with enhanced power-down mode

- A new, high-performance, on-chip, digital data separator without external filter

- A new, ingreprior maney, one components

Support for 5.25"/3.5" floppy disk drives

Automatic media sense support

Perpendicular recording drive support

Three mode Floppy Disk Drive (FDD) support

Full support for IBM? Tape Drive Register (TDR) implementation

Support for new fast tape drives (2 Mbps) and standard tape drives (1 Mbps, 500 Kbps and 250 Kbps) — Support for both FM and MFM modes.

- Two Serial Communication Controllers provide: Software compatibility with the 16550A and the 16450 A modifiable 13-bit address

- Ten IRQ channel options

- MIDI baud rate support

- Four 8-bit DMA channel options on SCC2

- Shadow register support UART write-only bits

- A fast universal Infrared interface on SCC2 sup-ports the following:

- Data rates of up to 115.2 Kbps (SIR)

A data rate of 1.152 Mbps (MIR)

A data rate of 4.0 Mbps (FIR)

- Selectable internal or external modulation/de-modulation (Sharp-IR)

- **—** Consumer Electronic IR mode

- A bidirectional parallel port that includes: <u>A modifiable 13-bit address</u>

- A motivative of the annel options

Four 8-bit DMA channel options

An Enhanced Parallel Port (EPP) compatible with version EPP 1.9 IEEE1284 An Enhanced Faraner for (EFT) compatible with version EFT 1.9 rEEET28 compliant), that also supports version EPP 1.7 of the Xir-com specification.

An Extended Capabilities Port (ECP) that is

IEEE1284 compliant, including level 2

Bidirectional data transfer under either soft-ware or hardware control

- **—** Compatibility with ISA, EISA, and MicroChannel parallel ports

- Multiplexing of additional external FDC signals on parallel port pins that enables use of an external Floppy Disk Drive (FDD)

- A protection circuit that prevents damage to the parallel port when an external printer powers up or operates at high voltages

- 14 mA output drivers

- Two general purpose pins for two programmable chip select signals can be programmed for game port control.

- An address decoder that:

- Selects all primary and secondary ISA ad-dresses, including OM1-4 and LPT1-3 Decodes up to 16 address bits

- Clock source:

- An internal clock multiplier generates all required internal frequencies.

A clock input source 14.318 MHz, 24 MHz, or 48 MHz may be selected

- Enhanced power management features: Special power-down configuration registers Enhanced programmable FDC command to trigger power down

- Programmable power-down and wake-up modes

- Two dedicated pins for FDC power management

- \_\_\_\_ Low power-down current consumption (typically for PC97338, 400 A for 3.3V

- and 600 **µ**A for 5V application)

- \_\_\_\_ Reduced pin leakage current

- \_\_\_\_ Low power CMOS technology

- \_\_\_\_ The ability to shut off clocks to either the entire chip or only to specific modules

- Mixed voltage support provides:

- \_\_\_\_ Standard 5 V operation

- \_\_\_\_ Low voltage 3.3 V operation

- \_\_\_\_\_ Simultaneous internal 3.3 V operation and reception or transmission to devices that have either 3.3 V or 5 V power supply

- 100-pin TQFP VJG package PC87338/PC97338

- Standby mode: control by software

**Default configuration:**

|                                       | IO address | IRQx | DRQx |

|---------------------------------------|------------|------|------|

| COM1                                  | 3F8-3FF    | 4    | -    |

| FIR/MIR/SIR/<br>SHARP ASK<br>( COM2 ) | 278-27F    | 3    | -    |

| PIO                                   | 378-37F    | 7    | -    |

| FDD                                   | 3F0-3FF    | 6    | 2    |

#### **Block Diagram**

### 0.8 PC CARD interface controller: TI1225

- PCI Bus Power Management Interface Specification 1.0 Compliant

- ACPI 1.0 Compliant

- Fully Compatible With the Intel 430TX (Mobile Triton II) Chipset Packaged in 208-Pin TQFP

- PCI Local Bus Specification Revision 2.1 Compliant

- 1995 PC Card Standard Compliant

- 3.3-V Core Logic With Universal PCI Interfaces Compatible With 3.3-V and 5-V

- PCI Signaling Environments

- Mix-and-Match 5-V/3.3-V PC Card16 Cards and 3.3-V CardBus Cards

- Supports Two PC Card or CardBus Slots With Hot Insertion and Removal

- Uses Serial Interface to TIE TPS2202/2206 Dual-Slot PC Card Power Switch

- Supports Burst Transfers to Maximize Data Throughput

- Supports Parallel PCI Interrupts, Parallel ISA IRQ and Parallel PCI Interrupts, Serial ISA IRQ With Parallel PCI Interrupts, and Serial ISA IRQ and PCI Interrupts

- Serial EEPROM Interface for Loading Subsystem ID and Subsystem Vendor ID

- Pipelined Architecture Allows Greater Than 130M-Bytes-Per-Second Throughput From CardBus to PCI and From PCI to CardBus

- Supports Up to Five General-Purpose I/Os

- Programmable Output Select for CLKRUN

- Multifunction PCI Device With Separate Configuration Space for Each Socket

- Five PCI Memory Windows and Two I/O Windows Available for Each PC Card16 Socket

- Two I/O Windows and Two Memory Windows Available to Each CardBus Socket

- Exchangeable Card Architecture (ExCA) Compatible Registers Are Mapped in Memory and I/O Space

- Intel 82365SL-DF Register Compatible

- Supports Distributed DMA (DDMA) and PC/PCI DMA

- Supports 16-Bit DMA on Both PC Card Sockets

- Supports Ring Indicate, SUSPEND, PCI CLKRUN, and CardBus CCLKRUN

- LED Activity Pins

- Supports PCI Bus Lock (LOCK)

- Advanced Submicron, Low-Power CMOS Technology

- For the Complete Data Sheet for PCI1220, Please See Literature #SCPS016

NOTE: The PC Card interface is 68 pins for CardBus and 16-bit PC Cards. In zoomed-video mode 23 pins are used for routing the zoomed video signals too the VGA controller.

### 0.9 Keyboard System: H8(3434) Universal Keyboard Controller

### CPU

- Two-way general register configuration.

- Eight 16-bit registers or Sixteen 8-bit registers.

- High-speed operation.

- Maximum clock rate : 16Mhz at 5V.

### Memory

— Include 32KB ROM and 1KB RAM.

### 16-bit free-running timer

- One 16-bit free-running counter.

- Two output-compare lines.

- Four input capture lines.

### 8-bit timer (2 channels)

— each channel has one 8-bit up-counter , two time constant registers

### **PWM timer (2 channels)**

- Resolution : 1/250.

- Duty cycle can be set from 0 to 100%.

### I<sup>2</sup>C bus interface ( one channel )

— Include single master mode and slave mode. Host interface ( HIF)

- 8-bit host interface port .

- Three host interrupt requests (HIRQ1,11,12).

**—** Regular and fast A20 gate output.

#### **Keyboard controller**

Controls a matrix-scan keyboard by providing a keyboard scan function with wake-up interrupts and sense ports. \_\_\_\_

#### A/D converter

- 10-bit resolution.

- 8 channels : single or scan mode (selectable ). \_\_\_\_

### D/A converter

- 8-bit resolution. \_\_\_\_

- 2 channels. \_\_\_\_

### Interrupts

- nine external interrupt lines : NMI#, IRQ0 to 7#. \_\_\_\_

- 26 on-chip interrupt sources.

#### **Power-down modes**

- Sleep mode.

- Software standby mode.

- Hardware standby mode.

- A single chip microcomputer.

- On-chip flash memory. Maximum 64-kbyte address space. Support three PS/2 port for external keyboard ,mouse and internal track pad.

- Support SMI, SCI trigger input.

- Cover switch.

- Battery charging control.

- Smart Battery monitoring . Control D/D system on/off.

•

- Fan control and LED indicator serial interface

- 100pin TQFP

#### 0.9 System BIOS

See software BIOS specification

#### 0.10 **Memory System**

Main Memory

- NEC uPD4564163/Mitsubishi M2V64S40BTP-7 32 MB SDRAM on board

- One chip memory size: 4Mx16bit .

- \_\_\_\_ Standard 54 pin TSOP package.

- Power supply:  $3 \pm 0.3V$

- \_ Operating power dissipation: MAX 468mW

- One 144pin S.O. DIMM sockets on Mother Board for expansion

- Supports JEDEC specification: 144 S.O. DIMM socket.

- Memory bus bandwidth: 64 bits

• Supports 32MB SDRAM on board (can support up to 64MB) and one 144pin SDRAM SO-DIMM memory module upgrading up to 128 MB. Here are some main memory system essential characteristics:

| <br>4Mx16bit on board        | 32M             |

|------------------------------|-----------------|

| <br>144-pin S.O. DIMM socket | 1               |

| <br>Memory Voltage           | $3.3V \pm 0.3V$ |

**Banks on DIMM**

#### 0.11 Interface

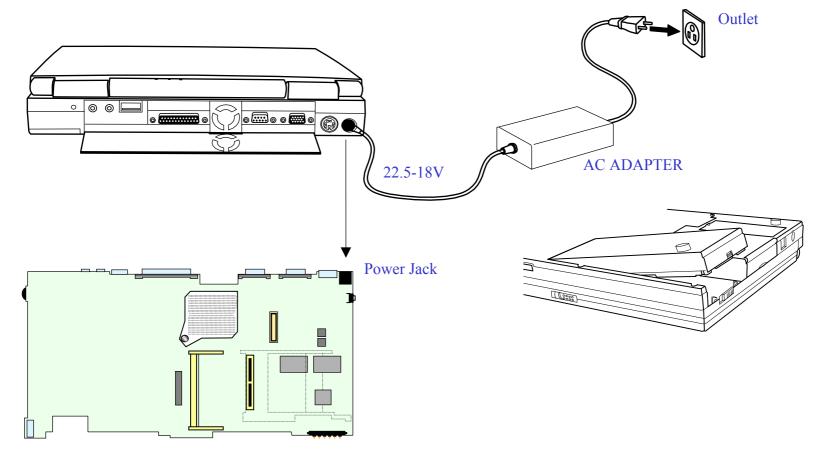

- **Power Supply Jack.**

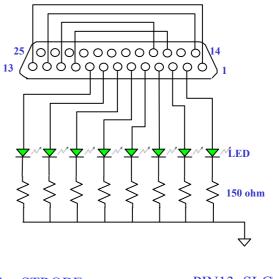

- **One Standard Parallel Port With ECP/EPP Functions**

- Two Serial Ports, One For COM1/COM2, The Other For • FIR/MIR/SIR/SHARP ASK

- **One External CRT Connector For CRT Display**

- One PS/2 Interface For External KB, Mouse Or Other Devices •

- **Two Cardbus Sockets**

- Connector For Connection Between M/B And Panel.

- . Y Connector For Connection Between M/B And LED BD, backlight BD.

- Headphone Out Jack And Microphone Input Jack.

- One MODEM RJ-11 phone jack for PSTN line. •

#### 0.12 Audio System : audio controller MAESTRO-2

- 64-voice wavetable synthesizer supporting DLS and 32 independent digital data streams Proprietary WaveCache Technology 3-D positional audio under DirectX?5.0 Enhanced effects (reverb, chorus, echo, vibrato, etc.) •

- .

- AC-3 decode acceleration

- External DSP for hardware AC-3 decode \_\_\_\_

- Active Movie AC-3 filter acceleration option

- 2- or 3-button hardware master volume control 1 2 S/Zoom Video support AC97 CODEC interface Up to 20-bit ADC/DAC audio resolution Complies with Microsoft ACPI rev 1.0 (D0~D3) & Advanced Power Management spec 1.2

- •

- 3.3 V power supply, 5 V I/O tolerant Supports up to 12 GPIO pins Secondary AC?7 CODEC interface .

- .

- PCI 2.1 bus master with scatter/gather support Distributed & PC/PCI DMA, Compaq/Intel serial IRQ support and Transparent DMA

#### 0.13 Audio System: AC' 97 CODEC CS4297

- An AC' 97 CODEC provides a complete high quality audio solution, Feature Include: \_\_\_\_\_\_\_MIDI port.

- MODÉM

- \_\_\_\_ **CD-ROM**

- \_\_\_\_ **User-Defined GPIO** \_\_\_\_

- Volume Control: Rotary VR

- Stereo BTL 2x1 W Amplifiers (TPA0202) With 8 Ohm Load. CD-ROM IDE Interface

- 16 Bit Stereo ADC & DAC For Record And Play Back Programmable Sample Rates From 4kHz To 44.1kHz For Record And Playback Microphone in \* 1 (3.5 mm phone-jack) Headphone out \* 1: stereo (3.5mm phone-jack) Built-in Speaker \* 2 (1w, 8 ohm) Built-in Microphone \* 1 Note the The Theorem Note the state of the table South Action State Terms and the state of the state of

- Note: For Those Input Source Not Using Should Be Set Mute In Order To Reduce Noise. Like Line In

#### 0.14 **FAX/MODEM** unit

.

- . Made by ASKEY Computer corporation

- .

- .

- Main chip : Pctel PCT789 Integrated PCI interface Host-based ITU V.70 DSVD.

- Video-ready modem interface (VRM) v.80

- **Operation** support:

- windows 95 windows NT

- K56flex for internet connection rates approaching 56kbits/s.

- **Data Modes capabilities**

- Ultrahigh compress throughput due to parallel access directly to the host PCITU-T V.34 extended rates: 33600 bits/s- 2400 bits/s V.32tero. V.32bis, and fallbacks

- **TIA-EIA 602 standard for AT command set** \_\_\_\_

- V.42 error correction (LAPM and MNP)

- FAX mode capabilities:

- ITU-T V.17, V.29, V.27ter, and V.21 CH 2 TIA/EIA 578 Class 1 FAX

- SIMULTALK full-duplex speakerphone (FDSP):

- Adaptive acoustic echo canceler for dynamic speaker/microphone positioning

- IS-101 AT+ V commands with extensions

- Hardware integrated:

- **Integrated DSP and interface device**

- **PCI** interface

- PCI but mastering for EDSP/DSVD/VRM

- Call progress speaker driver

- High-precision sigma-delta codec STLC7546: Integrated hybrid

- Extensive bit I/Os for homologation and cellular direct connect

- **Enhanced voice features:**

- **Telephone answering machine (TAM)** \_

- **Business audio (BA)** \_\_\_\_

- VoiceView \_\_\_\_

- Caller identification (caller ID)

- . Internal PLL for low-speed crystal support

- Autoconfiguration

- .

- Enhanced low-power modem Support for 5 V or 3.3 V power

#### 0.15 **FIR Port**

There is a IR port in 7233 system. The IR Port is compliant with IrDA 1.0, IrDA 1.1 and SHARP ASK specification and can support up to 4.0 Mb/s transfer rate.

- Fully Compliant to IrDA 1.1 Specifications 9.6 kb/s to 4 Mb/s operation

- Excellent nose-to-nose operation

- Typical Link Distance > 1.5 m Compatible with ASK, HP-SIR, and TV Remote IEC825-Class 1 Eye Safe •

- Wide Operating Voltage Range \_\_\_\_\_\_2.7 V to 5.25 V •

- Small Module Size 4.0 x 12.2 x 5.1 mm (HxWxD)

- Complete Shutdown TXD, RXD, PIN diode

- Low Shutdown Current

- 10 nA typical

- It is not typical

Adjustable Optical Power Management

Adjustable LED drive-current to maintain link integrity

Single Rx Data Output

FIR Select pin switch to FIR

Integrated EMI Shield

Excellent noise immunity

- Excellent holes immunity

Edge Detection Input

Prevents the LED from long turn-on time

Interface to Various Super I/O and Controller Devices

Designed to Accommodate Light Loss with Cosmetic Window

- Only 2 External Components are Required •

.

- Digital Imaging Digital Still Cameras

- **Photo-Imaging Printers**

- **Data Communication**

- \_\_\_\_

- Notebook Computers Desktop PCs Win CE Handheld Products

- Personal Digital Assistants (PDAs)

- Printers

- **Fax Machines, Photocopiers**

- **Screen Projectors**

- Auto PCs

- Dongles

- Set-Top Box

- Telecommunication Products Cellular Phones

- Pagers

- . **Small Industrial & Medical Instrumentation**

#### — General Data Collection Devices

## Patient & Pharmaceutical Data Collection Devices IR LANs

### 0.16 Mass Storage Sub-system

There is one 2.5", 8.45/9.5mm hard disk drive installed in 7233 system, which can support 3/4/6/9/12 GB, Ultra-DMA33 function.

### CD-ROM (24X speed) / DVD-ROM (6X speed)

7233 System has one standard CD-ROM (24 times speed or higher)/DVD-ROM (6 times speed or higher). The hardware interface is compliant with ATAPI IDE specification. The default drive is D. User should install the CD-ROM/DVD-ROM device driver in order to operate this device.

### 0.17 Special Feature Function

### **Key Function**

| Keys Combination | Feature                                | Meaning                                                                                           |

|------------------|----------------------------------------|---------------------------------------------------------------------------------------------------|

| Fn + F5          | LCD/external CRT<br>switching          | Rotate display mode in LCD only, CRT only and simultaneously display.                             |

| Fn + F6          | Brightness down                        | Decreases the LCD brightness / No function in<br>DSTN model                                       |

| Fn + F7          | Brightness up                          | Increases the LCD brightness / No function in DSTN model                                          |

| Fn + F8          | Contrast down                          | Decreases the LCD contrast                                                                        |

| Fn + F9          | Contrast up                            | Increase the LCD contrast                                                                         |

| Fn + F10         | Enable/Disable Battery<br>Warning Beep | Toggle Battery Warning on/off                                                                     |

| Fn + F11         | Panel Off/On                           | Toggle Panel Off/On                                                                               |

| Fn + F12         | Suspend to DRAM / HDD                  | Force the computer into either Suspend to HDD or<br>Suspend to DRAM mode depending on BIOS Setup. |

### Flash ROM (BIOS)

7233 system utilizes the state-of-the-art Flash EEPROM technology. User can upgrade the system BIOS in the future just running the program from MiTAC.

### **LED** Indicators

System has nine status LED indicators to display system activity which include below LCD panel unit and above keyboard:

1. Three LED indicators below LCD panel unit:

From left to right that indicate AC POWER, BATTERY POWER and BATTERY STATUS

- AC POWER: This LED lights green when the notebook is being powered by AC, and flash (on 1 second, off 1 second ) when Suspend to DRAM is active using AC power. The LED is off when the notebook is off or powered by batteries, or when Suspend to Disk.

- BATTERY POWER: This LED lights green when the notebook is being powered by batteries, and flashes (on 1 second, off 1 second) when Suspend to DRAM is active using battery power. The LED is off when the notebook is off or powered by AC, or when Suspend to Disk.

- BATTERY STATUS : During normal operation, this LED stays off as long as the battery is charged. When the battery charge drops to 10% of capacity, the LED lights red, flashes per 1 second and beeps per 2 second. When AC is connected, this indicator glows green if the battery pack is fully charged, or orange (amber) if the battery is being charged.

Six LED indicators above keyboard:

From left to right that indicates CD-ROM/DVD-ROM, HARD DISK DRIVE, FLOPPY DISK DRIVE, NUM LOCK, CAPS LOCK and SCROLL LOCK.

**COM port assignment**

COM1: MODEM / RS-232 / Disable COM2: IR / RS-232 / Disable

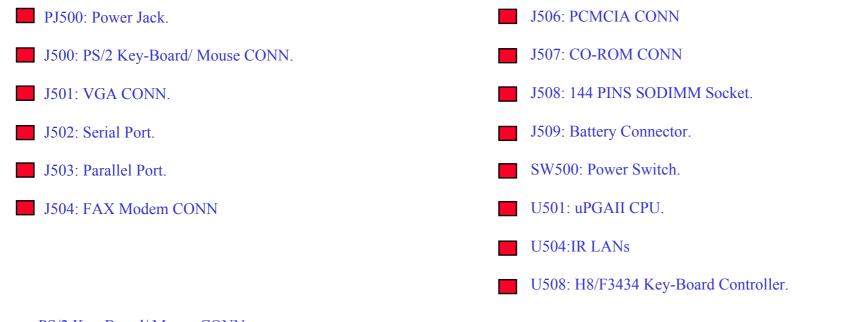

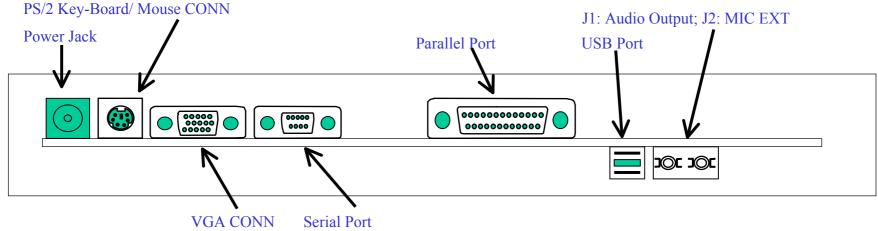

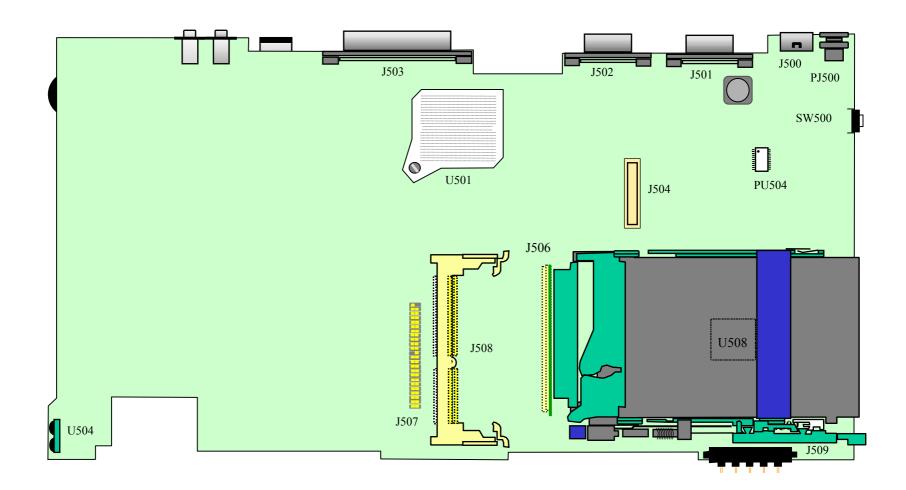

# 1. Definition & Location of Connectors/ Switches/Components (A)

| J1: Audio Output.                  | U8: CS4297 AC' 97 Compliant Audio Codec.   |

|------------------------------------|--------------------------------------------|

| J2: MIC EXT.                       | U9: PIIX4E(82371MB) South Bridge.          |

| J3: USB Port.                      | U11: ICS W137 Frequency Synthesizer.       |

| J4: Internal MIC CONN              | U12,U19: SGRAM.                            |

| J5/J7: L/R SPK CONN.               | U13: ATI_RAGE_LT PRO AGP VGA CTRL.         |

| J8: LCD Panel TRANS. BD Connector. | U14: 72466 Geyserville Speed Step.         |

| J9: Inverter BD CONN.              | U15: ESS MAESTRO-2E Audio Controller Chip. |

| J10: Keyboard CONN.                | U16,U22,U25,U30: 32MB On-Board Memory.     |

| J11: FDD CONN.                     | U20: NS PC93338VJG Supper I/O Controller.  |

| J12: Touch-pad/ HDD CONN.          | U21: FW82443BX Host Bridge Controller.     |

| SW1: Suspend Switch.               | U27: 32P/PLCC/SMT SYS BIOS.                |

| SW2: LCD ID/ Key Matrix Select.    | U28: TI 1225 PCI-PCMCIA/CARBUS Controller  |

| VR1: Volume Control VR.            | U29: W40S11-02 SDAM Clock Buffer.          |

## 2. Definition & Location of Connectors/Switches/Switches(A)

# 2. Definition & Location Major Components/connectors (Side B)

# 2. Definition & Location Major Components (Side B)

## 3. Pin Descriptions of Major Componts 3.1 Intel μPGAII CPU Processor-1

### **Alphabetical Signal Reference**

| Signal Name | I/O                   | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A[35:3]#    | I/O<br>GTL+           | The A[35:3]# (Address) signals define a 2 <sup>36</sup> -byte physical memory address space. When ADS# is active, these signals transmit the address of a transaction; when ADS# is inactive, these signals transmit transaction information. These signals must be connected to the appropriate pins/balls of both agents on the system bus. The A[35:24]# signals are protected with the AP1# parity signal, and the A[23:3]# signals are protected with the AP0# parity signal. On the active-to-inactive transition of RESET#, each processor bus agent samples A[35:3]# signals to determine its power-on configuration. See Section 4 of this document and the <i>PentiumII Processor Developer' s Manua</i> for details. |

| A20M#       | I<br>1.5V<br>Tolerant | If the A20M# (Address-20 Mask) input signal is asserted, the processor masks physical address bit 20 (A20#) before looking up a line in any internal cache and before driving a read/write transaction on the bus. Asserting A20M# emulates the 8086 processor's address wrap-around at the 1-Mbyte boundary. Assertion of A20M# is only supported in Real mode.                                                                                                                                                                                                                                                                                                                                                                |

| ADS#        | I/O<br>GTL+           | The ADS# (Address Strobe) signal is asserted to indicate the validity<br>of a transaction address on the A[35:3]# signals. Both bus agents<br>observe the ADS# activation to begin parity checking, protocol<br>checking, address decode, internal snoop or deferred reply ID match<br>operations associated with the new transaction. This signal must be<br>connected to the appropriate pins/balls on both agents on the system<br>bus.                                                                                                                                                                                                                                                                                      |

| AERR#       | I/O<br>GTL+           | The AERR# (Address Parity Error) signal is observed and driven by<br>both system bus agents, and if used, must be connected to the<br>appropriate pins/balls of both agents on the system bus. AERR#<br>observation is optionally enabled during power-on configuration; if<br>enabled, a valid assertion of AERR# aborts the current transaction.<br>If AERR# observation is disabled during power-on configuration, a<br>central agent may handle an assertion of AERR# as appropriate to the<br>error handling architecture of the system.                                                                                                                                                                                   |

| AP[1:0]#    | I/O<br>GTL+           | The AP[1:0]# (Address Parity) signals are driven by the request<br>initiator along with ADS#, A[35:3]#, REQ[4:0]# and RP#. AP1#<br>covers A[35:24]#. AP0# covers A[23:3]#. A correct parity signal is<br>high if an even number of covered signals are low and low if an odd<br>number of covered signals are low. This allows parity to be high when<br>all the covered signals are high. AP[1:0]# should be connected to the<br>appropriate pins/balls on both agents on the system bus.                                                                                                                                                                                                                                      |

| BCLK        | I<br>2.5V<br>Tolerant | The BCLK (Bus Clock) signal determines the system bus frequency.<br>Both system bus agents must receive this signal to drive their outputs<br>and latch their inputs on the BCLK rising edge. All external timing<br>parameters are specified with respect to the BCLK signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Signal Name | I/O  | Signal Description                                                                                                                            |

|-------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| BERR#       | I/O  | The BERR# (Bus Error) signal is asserted to indicate an                                                                                       |

|             | GTL+ | unrecoverable error without a bus protocol violation. It may be driver                                                                        |

|             |      | by either system bus agent and must be connected to the appropriate                                                                           |

|             |      | pins/balls of both agents, if used. However, the mobile Pentium III                                                                           |

|             |      | processors do not observe assertions of the BERR# signal.                                                                                     |

|             |      | BERR# assertion conditions are defined by the system configuration.                                                                           |

|             |      | Configuration options enable the BERR# driver as follows:<br>• Enabled or disabled                                                            |

|             |      | Asserted optionally for internal errors along with IERR#                                                                                      |

|             |      | • Asserted optionally by the request initiator of a bus transaction after                                                                     |

|             |      | it observes an error                                                                                                                          |

|             |      | • Asserted by any bus agent when it observes an error in a bus                                                                                |

|             |      | transaction                                                                                                                                   |

| BINIT#      | I/O- | The BINIT# (Bus Initialization) signal may be observed and driven                                                                             |

|             | GTL+ | by both system bus agents and must be connected to the appropriate                                                                            |

|             |      | pins/balls of both agents, if used. If the BINIT# driver is enabled                                                                           |

|             |      | during the power-on configuration, BINIT# is asserted to signal any                                                                           |

|             |      | bus condition that prevents reliable future information.                                                                                      |

|             |      | If BINIT# is enabled during power-on configuration, and BINIT# is                                                                             |

|             |      | sampled asserted, all bus state machines are reset and any data which                                                                         |

|             |      | was in transit is lost. All agents reset their rotating ID for bus<br>arbitration to the state after reset, and internal count information is |

|             |      | lost. The L1 and L2 caches are not affected.                                                                                                  |

|             |      | If BINIT# is disabled during power-on configuration, a central agent                                                                          |

|             |      | may handle an assertion of BINIT# as appropriate to the Machine                                                                               |

|             |      | Check Architecture (MCA) of the system.                                                                                                       |

| BNR#        | I/O- | The BNR# (Block Next Request) signal is used to assert a bus stall by                                                                         |

|             | GTL+ | any bus agent that is unable to accept new bus transactions. During a                                                                         |

|             |      | bus stall, the current bus owner cannot issue any new transactions.                                                                           |

|             |      | Since multiple agents may need to request a bus stall simultaneously,                                                                         |

|             |      | BNR# is a wired-OR signal that must be connected to the appropriate                                                                           |

|             |      | pins/balls of both agents on the system bus. In order to avoid wire-OF                                                                        |

|             |      | glitches associated with simultaneous edge transitions driven by                                                                              |

|             |      | multiple drivers, BNR# is activated on specific clock edges and sampled on specific clock edges.                                              |

| BP[3:2]#    | I/O  | The BP[3:2]# (Breakpoint) signals are the System Support group                                                                                |

| DI [J.2]#   | GTL+ | Breakpoint signals. They are outputs from the processor that indicate                                                                         |

|             |      | the status of breakpoints.                                                                                                                    |

| BPM[1:0]#   | I/O  | The BPM[1:0]# (Breakpoint Monitor) signals are breakpoint and                                                                                 |

| . ,         | GTL+ | performance monitor signals. They are outputs from the processor                                                                              |

|             |      | that indicate the status of breakpoints and programmable counters                                                                             |

|             |      | used for monitoring processor performance.                                                                                                    |

## 3.1 Intel µPGAII CPU Processor-2

### **Alphabetical Signal Reference**

| Signal Name | I/O      | Signal Description                                                                                                                          |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------|

| BPRI#       | Ι        | The BPRI# (Bus Priority Request) signal is used to arbitrate for                                                                            |

|             | GTL+     | ownership of the system bus. It must be connected to the appropriate                                                                        |

|             |          | pins/balls on both agents on the system bus. Observing BPRI# active                                                                         |

|             |          | (as asserted by the priority agent) causes the processor to stop issuing                                                                    |

|             |          | new requests, unless such requests are part of an ongoing locked                                                                            |

|             |          | operation. The priority agent keeps BPRI# asserted until all of its                                                                         |

|             |          | requests are completed and then releases the bus by deasserting BPRI#.                                                                      |

| BREQ0#      | I/O      | The BREQ0# (Bus Request) signal is a processor Arbitration Bus                                                                              |

|             | GTL+     | signal. The processor indicates that it wants ownership of the system                                                                       |

|             |          | bus by asserting the BREQ0# signal.                                                                                                         |

|             |          | During power-up configuration, the central agent must assert the                                                                            |

|             |          | BREQ0# bus signal. The processor samples BREQ0# on the active-                                                                              |

|             |          | to-inactive transition of RESET#.                                                                                                           |

| BSEL[1:0]   | I        | The BSEL[1:0] (Select Processor System Bus Speed) signal is used to                                                                         |

|             | 1.5V     | configure the processor for the system bus frequency. Table 38 shows                                                                        |

|             | Iolerant | the encoding scheme for BSEL[1:0]. The only supported system bus                                                                            |

|             |          | frequency for the mobile Pentium III processor is 100 MHz. If                                                                               |

|             |          | another frequency is used or if the BSEL[1:0] signals are not driven<br>with "1" then the processor is not guaranteed to function properly. |

|             |          | BSEL[1:0] Encoding                                                                                                                          |

|             |          | BSEL[1:0] System Bus Frequency                                                                                                              |

|             |          | 00 66 MHz                                                                                                                                   |

|             |          | 01 100 MHz                                                                                                                                  |

|             |          | 10 Reserved                                                                                                                                 |

|             |          | 11 133 MHz                                                                                                                                  |

| CLKREF      | Analog   | The CLKREF (System Bus Clock Reference) signal provides a                                                                                   |

|             | _        | reference voltage to define the trip point for the BCLK signal. This                                                                        |

|             |          | signal should be connected to a resistor divider to generate 1.25V                                                                          |

|             |          | from the 2.5-V supply.                                                                                                                      |

| CMOSREF     | Analog   | The CMOSREF (CMOS Reference Voltage) signal provides a DC                                                                                   |

|             |          | level reference voltage for the CMOS input buffers. A voltage divider                                                                       |

|             |          | should be used to divide a stable voltage plane (e.g., 2.5V or 3.3V).                                                                       |

|             |          | This signal must be provided with a DC voltage that meets the                                                                               |

| D/(2.0)//   | 1/0      | VCMOSREF specification from Table 13.                                                                                                       |

| D[63:0]#    | I/O      | The D[63:0]# (Data) signals are the data signals. These signals                                                                             |

|             | GTL+     | provide a 64-bit data path between both system bus agents, and must                                                                         |

|             |          | be connected to the appropriate pins/balls on both agents. The data driver asserts DRDY# to indicate a valid data transfer.                 |

|             |          | unver assents DKDY# to indicate a valid data transfer.                                                                                      |

| Signal Name | I/O          | Signal Description                                                                                                                 |

|-------------|--------------|------------------------------------------------------------------------------------------------------------------------------------|

| DBSY#       | I/O-<br>GTL+ | The DBSY# (Data Bus Busy) signal is asserted by the agent responsible for driving data on the system bus to indicate that the data |

|             |              | bus is in use. The data bus is released after DBSY# is deasserted. This                                                            |

|             |              | signal must be connected to the appropriate pins/balls on both agents<br>on the system bus.                                        |

| DEFER#      | I            | The DEFER# (Defer) signal is asserted by an agent to indicate that                                                                 |

|             | GTL+         | the transaction cannot be guaranteed in-order completion. Assertion                                                                |

|             |              | of DEFER# is normally the responsibility of the addressed memory                                                                   |

|             |              | agent or I/O agent. This signal must be connected to the appropriate                                                               |

|             | 1/0          | pins/balls on both agents on the system bus.                                                                                       |

| DEP[7:0]#   | I/O<br>GTL+  | The DEP[7:0]# (Data Bus ECC Protection) signals provide optional ECC protection for the data bus. They are driven by the agent     |

|             | GILT         | responsible for driving D[63:0]#, and must be connected to the                                                                     |

|             |              | appropriate pins/balls on both agents on the system bus if they are                                                                |

|             |              | used. During power-on configuration, DEP[7:0]# signals can be                                                                      |

|             |              | enabled for ECC checking or disabled for no checking.                                                                              |

| DRDY#       | I/O          | The DRDY# (Data Ready) signal is asserted by the data driver on                                                                    |

|             | GTL+         | each data transfer, indicating valid data on the data bus. In a multi-                                                             |

|             |              | cycle data transfer, DRDY# can be deasserted to insert idle clocks.                                                                |

|             |              | This signal must be connected to the appropriate pins/balls on both                                                                |

|             |              | agents on the system bus.                                                                                                          |

| EDGCTRLP    | Analog       |                                                                                                                                    |

|             |              | edge rate of the GTL+ output buffers. Connect the signal to VSS with a $110-\pounds$ [1% resistor.                                 |

| FERR#       | 0            | The FERR# (Floating-point Error) signal is asserted when the                                                                       |

| FEKK#       | 1.5V         | processor detects an unmasked floating-point error. FERR# is similar                                                               |

|             |              | to the ERROR# signal on the Intel 387 coprocessor, and it is included                                                              |

|             | Open-        | for compatibility with systems using DOS-type floating-point error                                                                 |

|             | drain)       | reporting.                                                                                                                         |

| FLUSH#      | I            | When the FLUSH# (Flush) input signal is asserted, the processor                                                                    |

|             | 1.5V         | writes back all internal cache lines in the Modified state and                                                                     |

|             | Tolerant     | invalidates all internal cache lines. At the completion of a flush                                                                 |

|             |              | operation, the processor issues a Flush Acknowledge transaction. The                                                               |

|             |              | processor stops caching any new data while the FLUSH# signal                                                                       |

|             |              | remains asserted.                                                                                                                  |

|             |              | On the active-to-inactive transition of RESET#, each processor bus agent samples FLUSH# to determine its power-on configuration.   |

|             |              | agent samples r 10.011# to determine its power-on configuration.                                                                   |

## 3.1 Intel µPGAII CPU Processor-3

### **Alphabetical Signal Reference**

| Signal Name | I/O      | Signal Description                                                       |

|-------------|----------|--------------------------------------------------------------------------|

| GHI#        | Ι        | The GHI# signal controls which operating mode bus ratio is selected      |

|             |          | in a mobile Pentium III processor featuring Intel SpeedStep              |

|             | Tolerant | technology. On the processor featuring Intel SpeedStep technology,       |

|             |          | this signal is latched when BCLK restarts in Deep Sleep state and        |

|             |          | determines which of two bus ratios is selected for operation. This       |

|             |          | signal is ignored when the processor is not in the Deep Sleep state.     |

|             |          | This signal is a "Don't Care" on processors that do not feature Intel    |

|             |          | SpeedStep technology. This signal has an on-die pull-up to VccT and      |

|             |          | should be driven with an Open-drain driver with no external pull-up.     |

| HIT#, HITM# | I/O      | The HIT# (Snoop Hit) and HITM# (Hit Modified) signals convey             |

|             | GTL+     | transaction snoop operation results, and must be connected to the        |

|             |          | appropriate pins/balls on both agents on the system bus.                 |

|             |          | Either bus agent can assert both HIT# and HITM# together to indicate     |

|             |          | that it requires a snoop stall, which can be continued by reasserting    |

|             |          | HIT# and HITM# together.                                                 |

| IERR#       | 0        | The IERR# (Internal Error) signal is asserted by the processor as the    |

|             | 1.5V     | result of an internal error. Assertion of IERR# is usually accompanied   |

|             |          | by a SHUTDOWN transaction on the system bus.                             |

|             | Open-    | This transaction may optionally be converted to an external error        |

|             | drain    | signal (e.g., NMI) by system logic. The processor will keep IERR#        |

|             |          | asserted until it is handled in software or with the assertion of        |

|             |          | RESET#, BINIT, or INIT#.                                                 |

| IGNNE#      | Ι        | The IGNNE# (Ignore Numeric Error) signal is asserted to force the        |

|             |          | processor to ignore a numeric error and continue to execute non-         |

|             | Tolerant | control floating-point instructions. If IGNNE# is deasserted, the        |

|             |          | processor freezes on a non-control floating-point instruction if a       |

|             |          | previous instruction caused an error. IGNNE# has no affect when the      |

|             |          | NE bit in control register 0 (CR0) is set.                               |

| INIT#       | I        | The INIT# (Initialization) signal is asserted to reset integer registers |

|             |          | inside the processor without affecting the internal (L1 or L2) caches    |

|             | Tolerant | or the floating-point registers. The processor begins execution at the   |

|             |          | power-on reset vector configured during power-on configuration. The      |

|             |          | processor continues to handle snoop requests during INIT# assertion.     |

|             |          | INIT# is an asynchronous input.                                          |

|             |          | If INIT# is sampled active on RESET#'s active-to-inactive transition,    |

|             |          | then the processor executes its built-in self test (BIST).               |

| Signal Name | I/O       | Signal Description                                                     |

|-------------|-----------|------------------------------------------------------------------------|

| INTR        | Ι         | The INTR (Interrupt) signal indicates that an external interrupt has   |

|             | 1.5V      | been generated. INTR becomes the LINTO signal when the APIC is         |

|             | Tolerant  | enabled. The interrupt is maskable using the IF bit in the EFLAGS      |

|             |           | register. If the IF bit is set, the processor vectors to the interrupt |

|             |           | handler after completing the current instruction execution. Upon       |

|             |           | recognizing the interrupt request, the processor issues a single       |

|             |           | Interrupt Acknowledge (INTA) bus transaction. INTR must remain         |

|             |           | active until the INTA bus transaction to guarantee its recognition.    |

| LINT[1:0]   | I         | The LINT[1:0] (Local APIC Interrupt) signals must be connected to      |

|             | 1.5V      | the appropriate pins/balls of all APIC bus agents, including the       |

|             |           | processor and the system logic or I/O APIC component. When APIC        |

|             | Tototaint | is disabled, the LINTO signal becomes INTR, a maskable interrupt       |

|             |           | request signal, and LINT1 becomes NMI, a non-maskable interrupt.       |

|             |           | INTR and NMI are backward compatible with the same signals for         |

|             |           | the Pentium processor. Both signals are asynchronous inputs.           |

|             |           | Both of these signals must be software configured by programming       |

|             |           | the APIC register space to be used either as NMI/INTR or LINT[1:0]     |

|             |           | in the BIOS. If the APIC is enabled at reset, then LINT[1:0] is the    |

|             |           | default configuration.                                                 |

| LOCK#       | I/O       | The LOCK# (Lock) signal indicates to the system that a sequence of     |

| LOCIN       | GTL+      | transactions must occur atomically. This signal must be connected to   |

|             | 012       | the appropriate pins/balls on both agents on the system bus. For a     |

|             |           | locked sequence of transactions, LOCK# is asserted from the            |

|             |           | beginning of the first transaction through the end of the last         |

|             |           | transaction                                                            |

|             |           | When the priority agent asserts BPRI# to arbitrate for bus ownership,  |

|             |           | it waits until it observes LOCK# deasserted. This enables the          |

|             |           | processor to retain bus ownership throughout the bus locked operation  |

|             |           | and guarantee the atomicity of lock.                                   |

| NMI         | Ι         | The NMI (Non-Maskable Interrupt) indicates that an external            |

|             | 1.5V      | interrupt has been generated. NMI becomes the LINT1 signal when        |

|             |           | the APIC is disabled. Asserting NMI causes an interrupt with an        |

|             |           | internally supplied vector value of 2. An external interrupt-          |

|             |           | acknowledge transaction is not generated. If NMI is asserted during    |

|             |           | the execution of an NMI service routine, it remains pending and is     |

|             |           | recognized after the IRET is executed by the NMI service routine. At   |

|             |           | most, one assertion of NMI is held pending. NMI is rising edge         |

|             |           | sensitive.                                                             |

### 3.1 Intel µPGAII CPU Processor-4

### **Alphabetical Signal Reference**

| Signal Name | I/O      | Signal Description                                                       |

|-------------|----------|--------------------------------------------------------------------------|

| PICCLK      | Ι        | The PICCLK (APIC Clock) signal is an input clock to the processor        |

|             | 2.5V     | and system logic or I/O APIC that is required for operation of the       |

|             | Tolerant | processor, system logic, and I/O APIC components on the APIC bus.        |

| PICD[1:0]   | I/O      | The PICD[1:0] (APIC Data) signals are used for bi-directional serial     |

|             | 1.5V     | message passing on the APIC bus. They must be connected to the           |

|             | Tolerant | appropriate pins/balls of all APIC bus agents, including the processor   |

|             | Open-    | and the system logic or I/O APIC components. If the PICD0 signal is      |

|             | drain    | sampled low on the active-to-inactive transition of the RESET#           |

|             |          | signal, then the APIC is hardware disabled.                              |

| PLL1, PLL2  | Analog   | The PLL1 and PLL2 signals provide isolated analog decoupling is          |

|             |          | required for the internal PLL. See Section 3.2.2 for a description of    |

|             |          | the analog decoupling circuit.                                           |

| PRDY#       | 0        | The PRDY# (Probe Ready) signal is a processor output used by             |

|             | GTL+     | debug tools to determine processor debug readiness.                      |

| PREQ#       | Ι        | The PREQ# (Probe Request) signal is used by debug tools to request       |

|             | 1.5V     | debug operation of the processor.                                        |

|             | Tolerant |                                                                          |

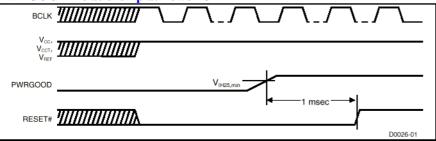

| PWRGOOD     | Ι        | PWRGOOD (Power Good) is a 2.5-V tolerant input. The processor            |

|             |          | requires this signal to be a clean indication that clocks and the power  |

|             | Tolerant | supplies (Vcc, VccT, etc.) are stable and within their specifications.   |

|             |          | Clean implies that the signal will remain low, (capable of sinking       |

|             |          | leakage current) and without glitches, from the time that the power      |

|             |          | supplies are turned on, until they come within specification. The        |

|             |          | signal will then transition monotonically to a high (2.5V) state. Figure |

|             |          | 26 illustrates the relationship of PWRGOOD to other system signals.      |

|             |          | PWRGOOD can be driven inactive at any time, but clocks and power         |

|             |          | must again be stable before the rising edge of PWRGOOD. It must          |

|             |          | also meet the minimum pulse width specified in Table 17 (Section         |

|             |          | 3.7) and be followed by a 1 ms RESET# pulse.                             |

### **PWRGOOD Relationship at Power On**

### **PWRGOOD Relationship at Power On**

The PWRGOOD signal, which must be supplied to the processor, is used to protect internal circuits against voltage sequencing issues. The PWRGOOD signal should be driven high throughout boundary scan operation.

| Signal Name | I/O         | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |