| 1. DEFINITION & LOCATION CONNECTORS/ SWITCHES | P. 2 |

|-----------------------------------------------|------|

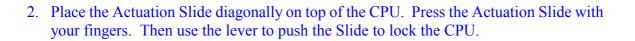

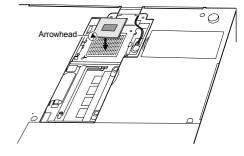

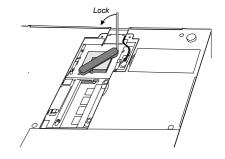

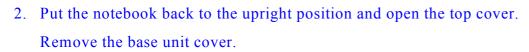

| 2. DEFINITION & LOCATION MAJOR COMPONENTS     | P. 4 |

| 3. PIN DESCRIPTIONS OF MAJOR COMPONENTS       | P. 6 |

| 4. SWITCH SETTING                             | P.32 |

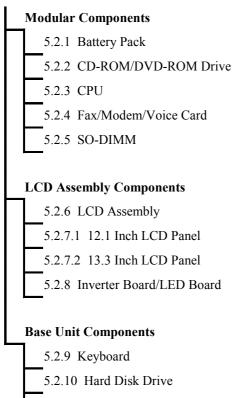

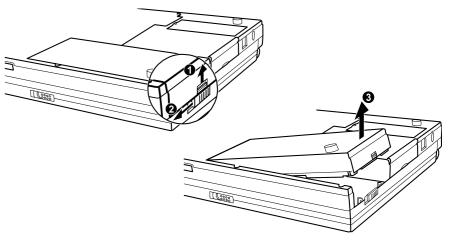

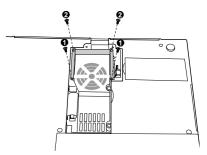

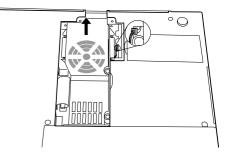

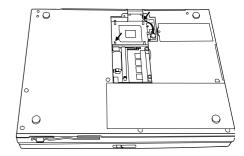

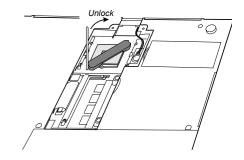

| 5. ASSEMBLY & DISASSEMBLY                     | P.33 |

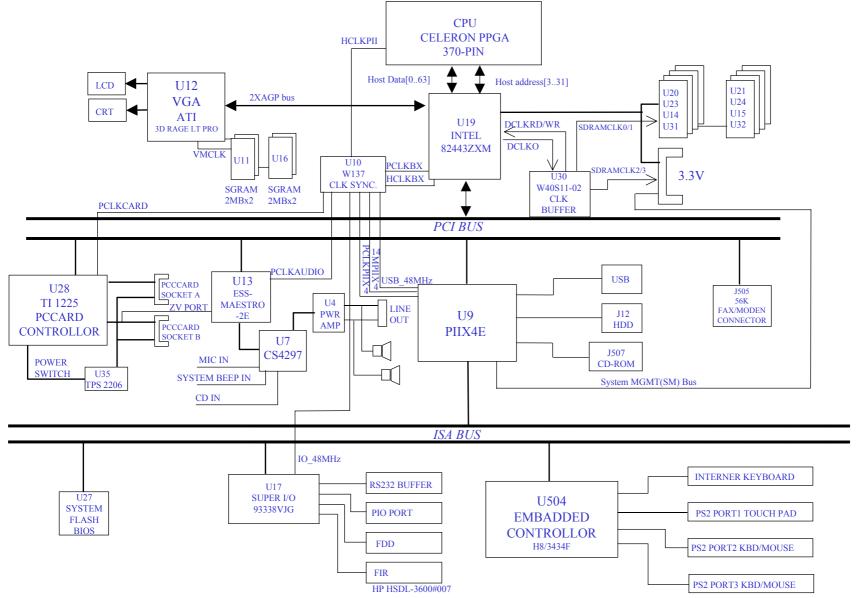

| 6. 6233 BLOCK DIAGRAM                         | P.55 |

| 7. MAINTENANCE DIAGNOSTICS                    | P.56 |

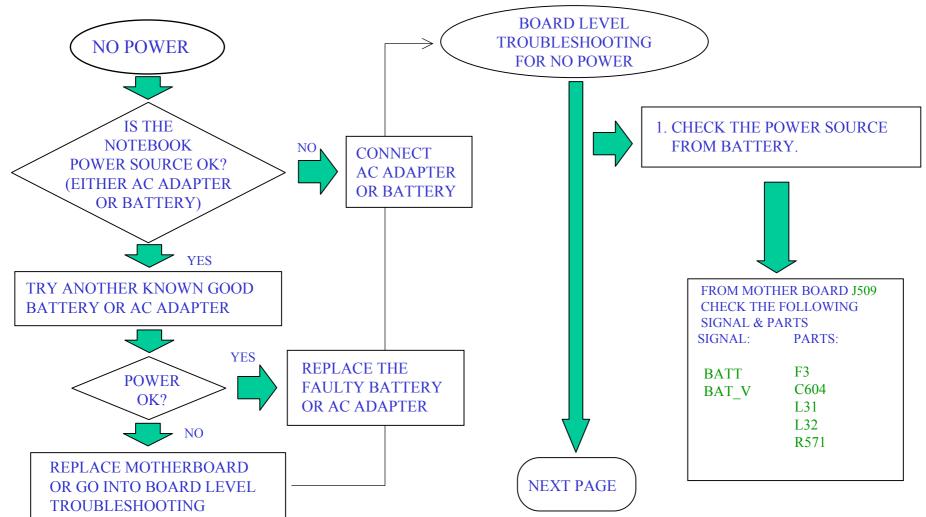

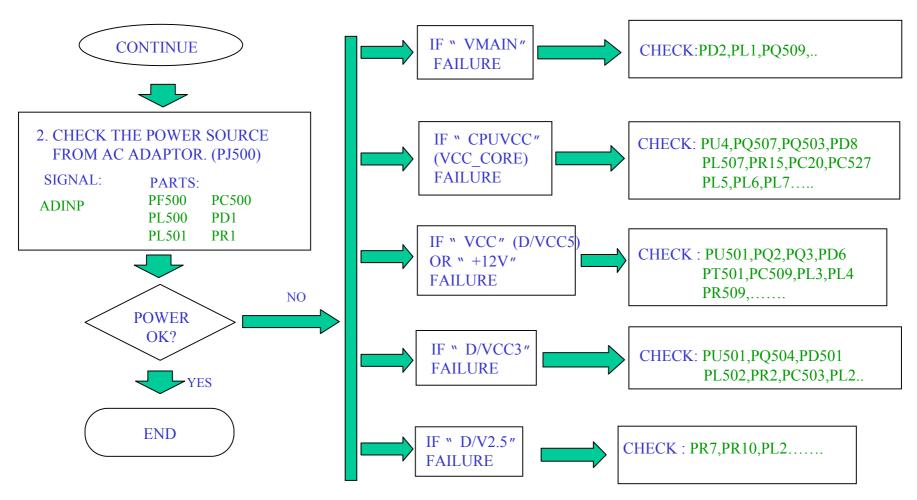

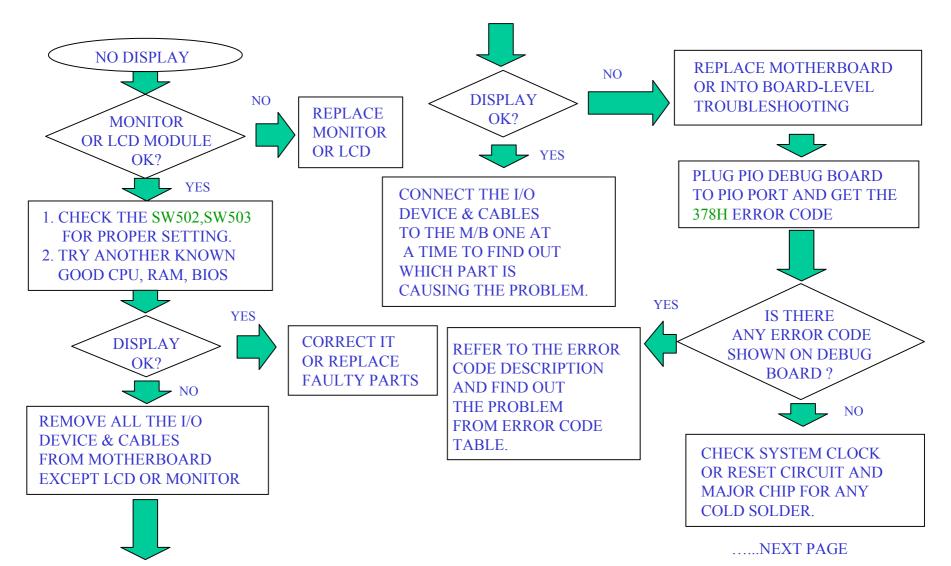

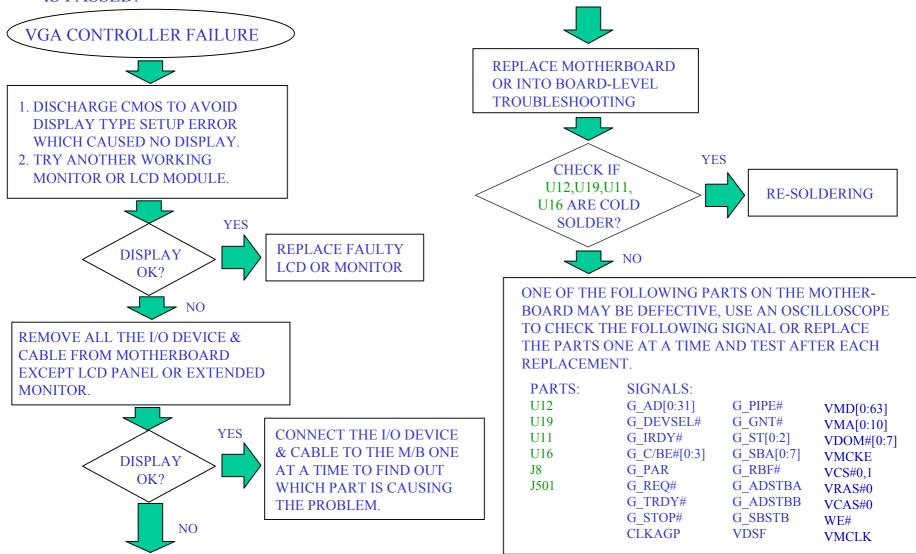

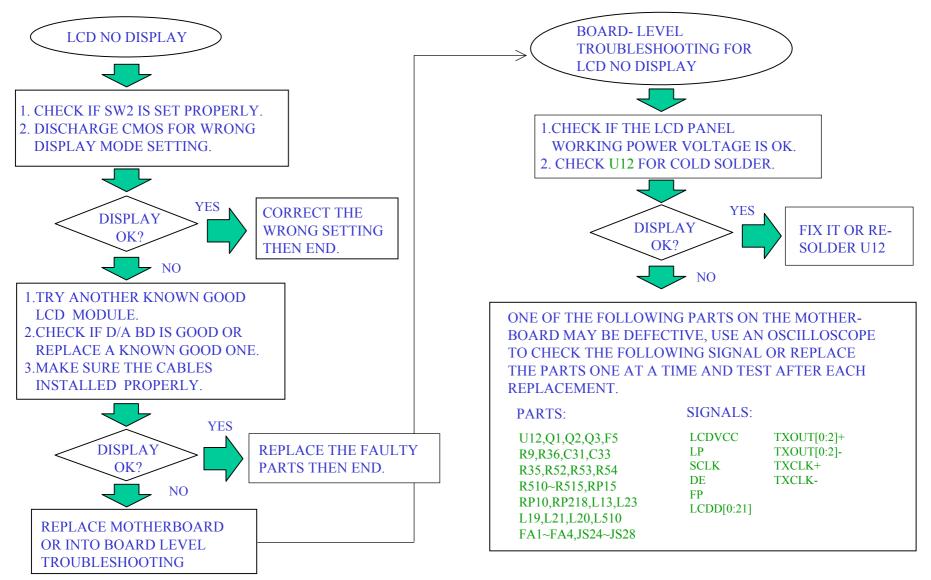

| 8. TROUBLE SHOOTING                           | P.59 |

| 9. SPARE PARTS LIST                           | P.92 |

| 10. CIRCUIT DIAGRAM                           | P.98 |

1

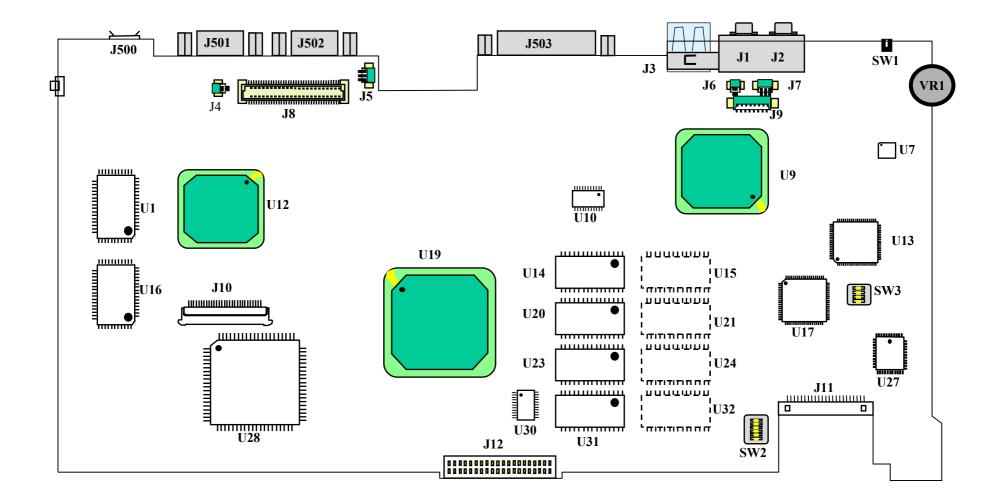

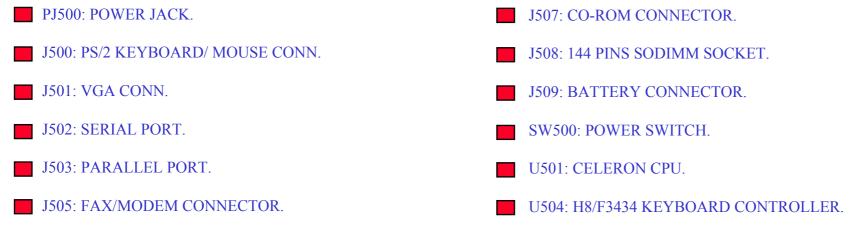

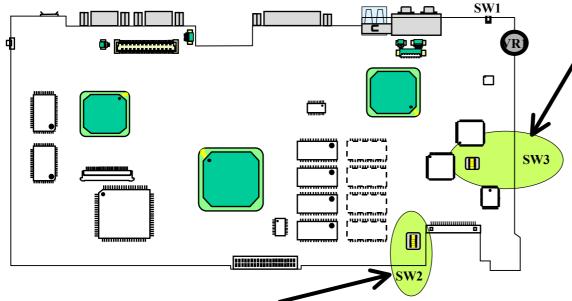

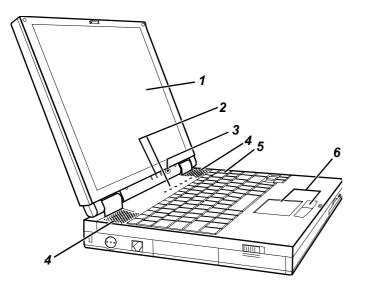

## **1. DEFINITION & LOCATION OF CONNECTORS / SWITCHES (A)**

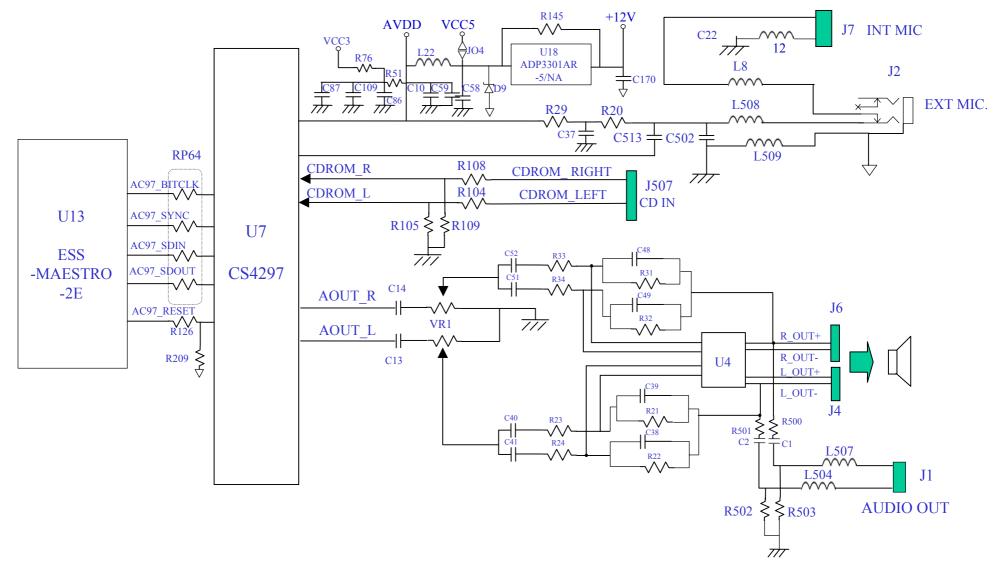

- J1: AUDIO OUTPUT.

- J2: MIC EXT.

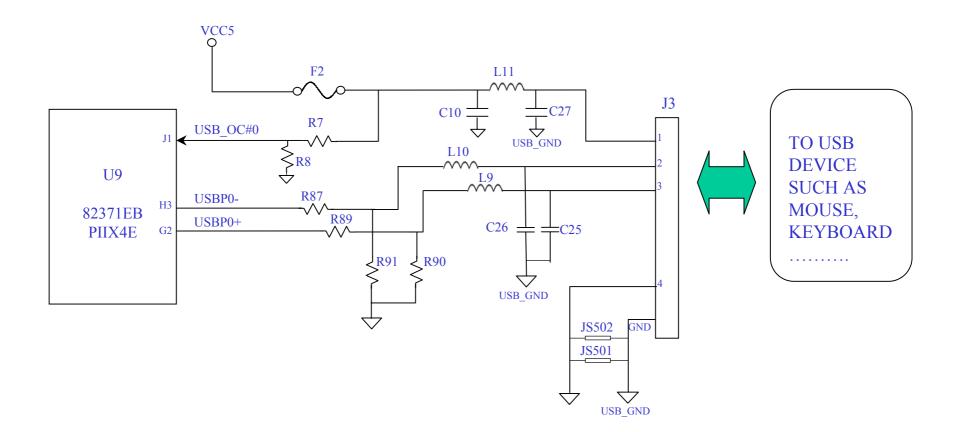

- J3: USB PORT.

- J4,J6: R/L SPK CONN.

- J5: CPU FAN CONN.

- J7: INTERNAL MIC CONN.

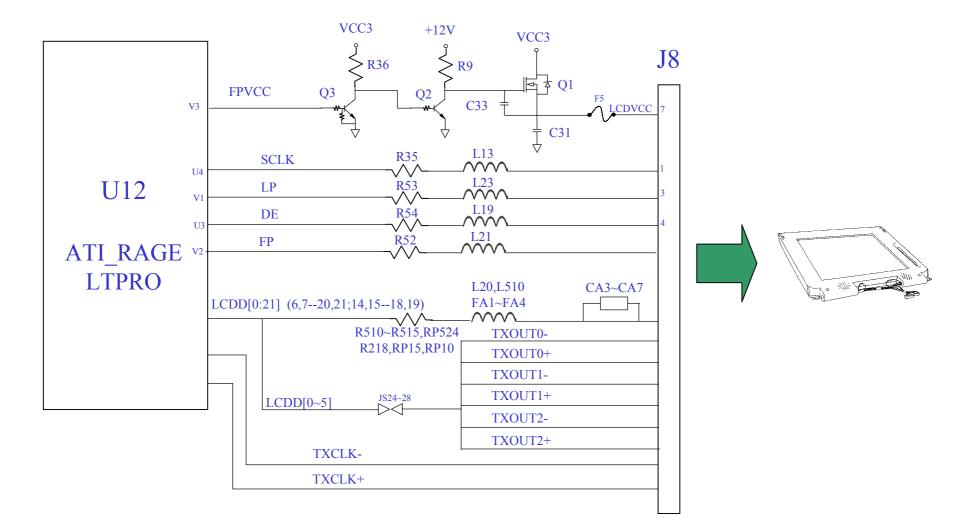

- J8: LCD PANEL TRANS. BD CONNECTOR.

- J9: INVERTER BD CONN.

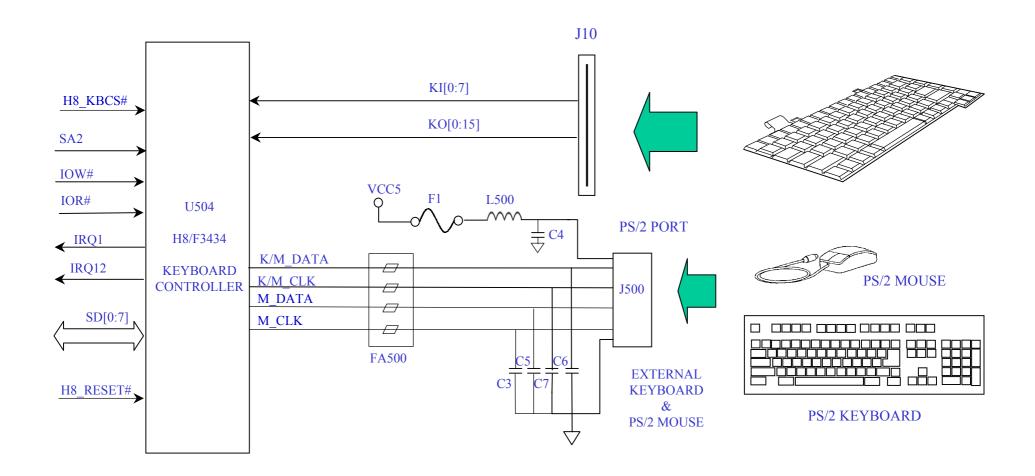

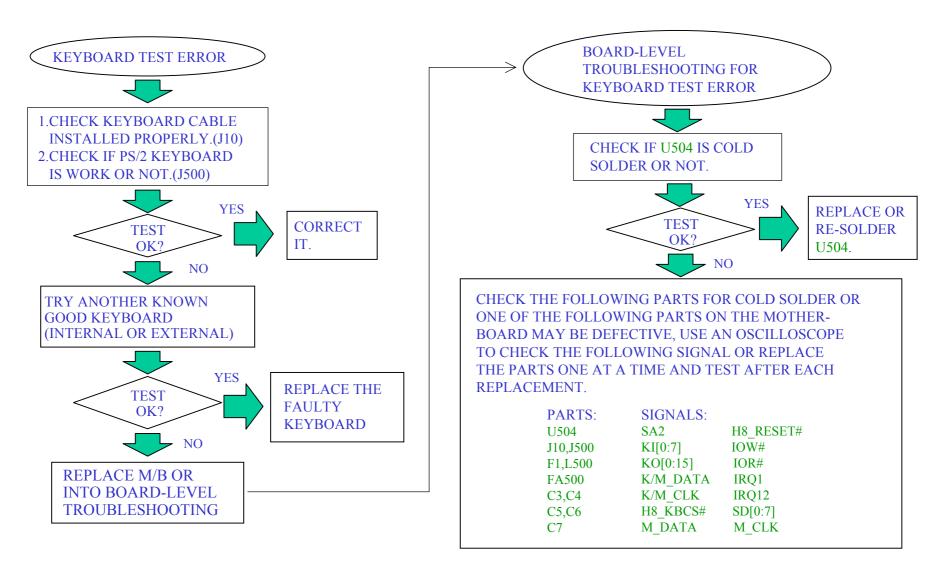

- J10: KEYBOARD CONN.

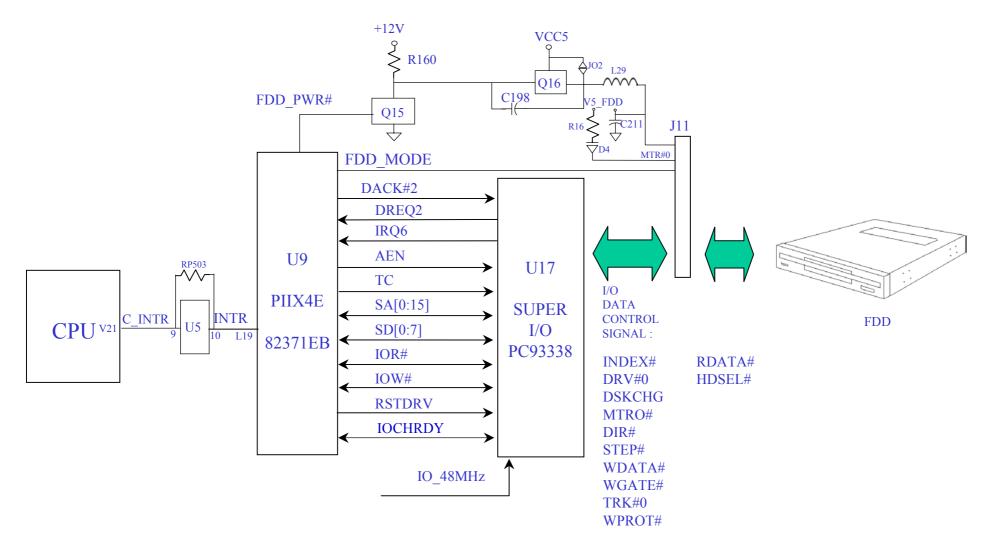

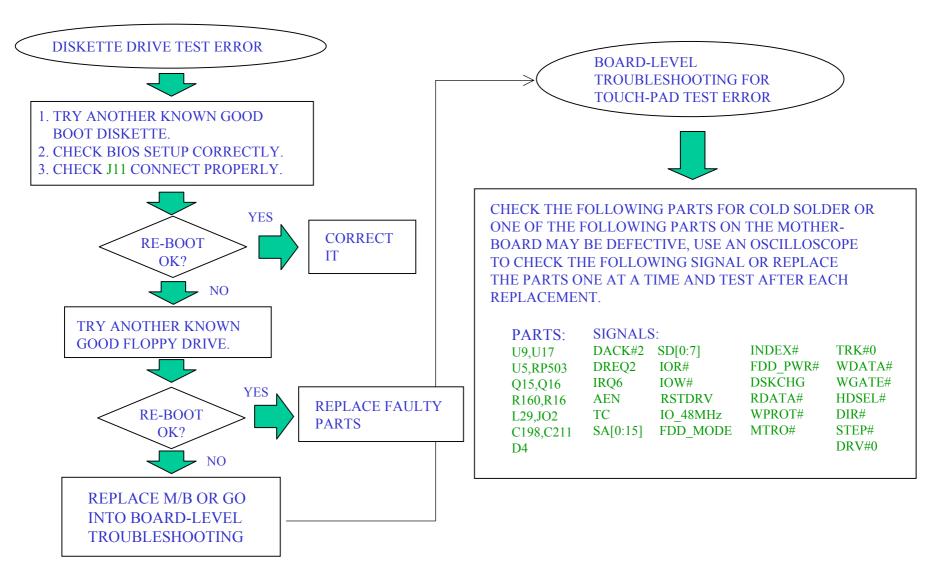

- J11: FDD CONN.

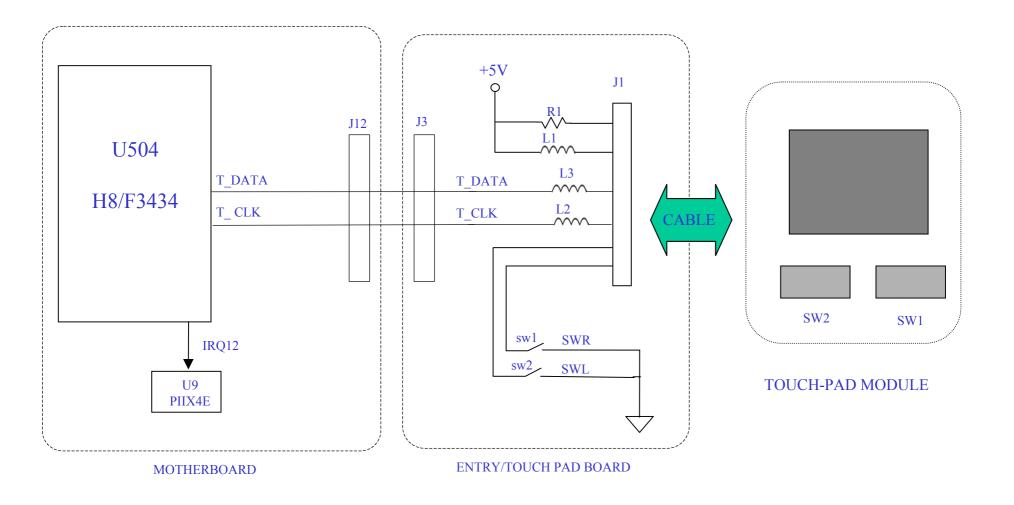

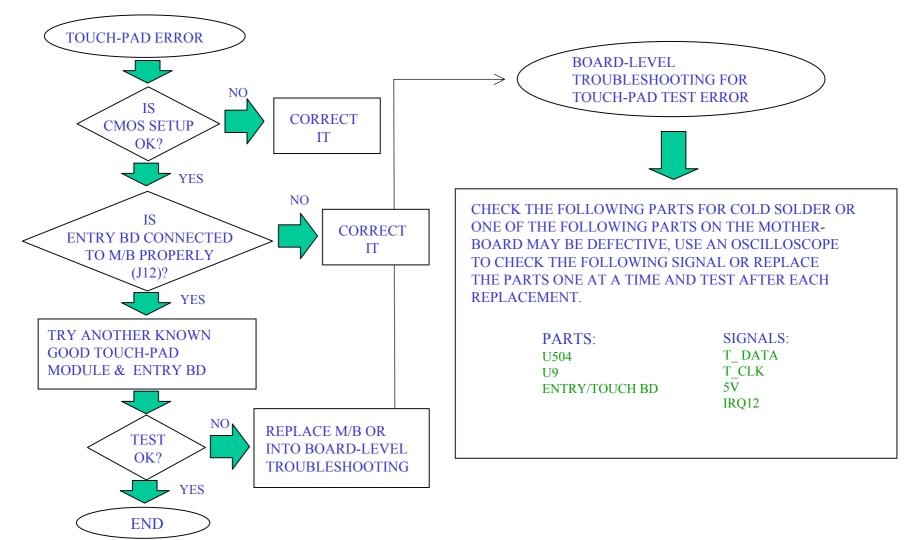

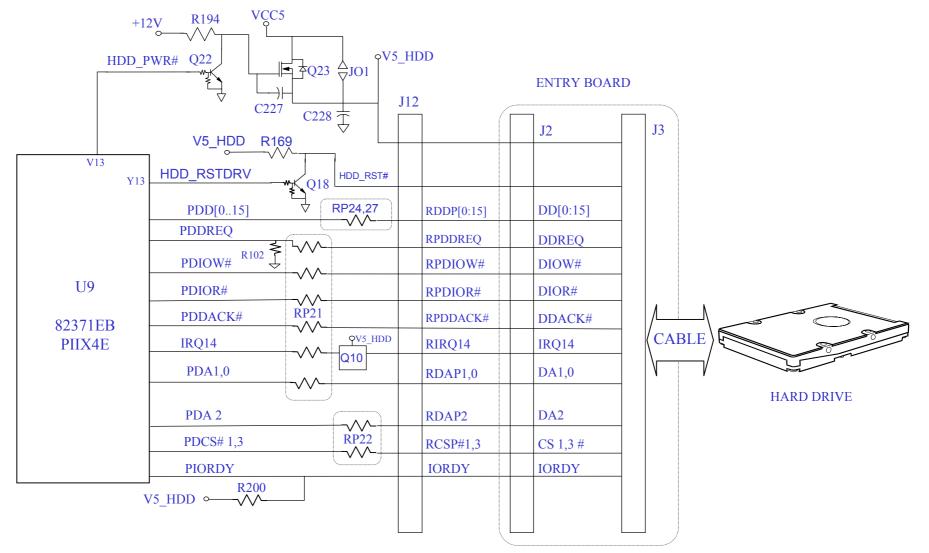

- J12: TOUCHPAD/ HDD CONN.

- SW1: SUSPEND SWITCH.

- SW2: LCD ID/ KEY MATRIX SELECT.

- SW3: CPU SPEED SEETING

- VR1: VOLUME CONTROL VR.

- U7:CS4297 AC 97 COMPLIANT AUDIO CODEC.

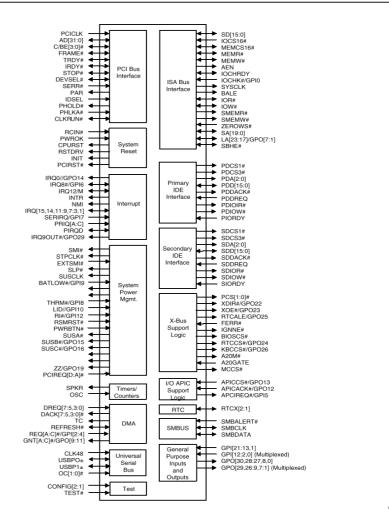

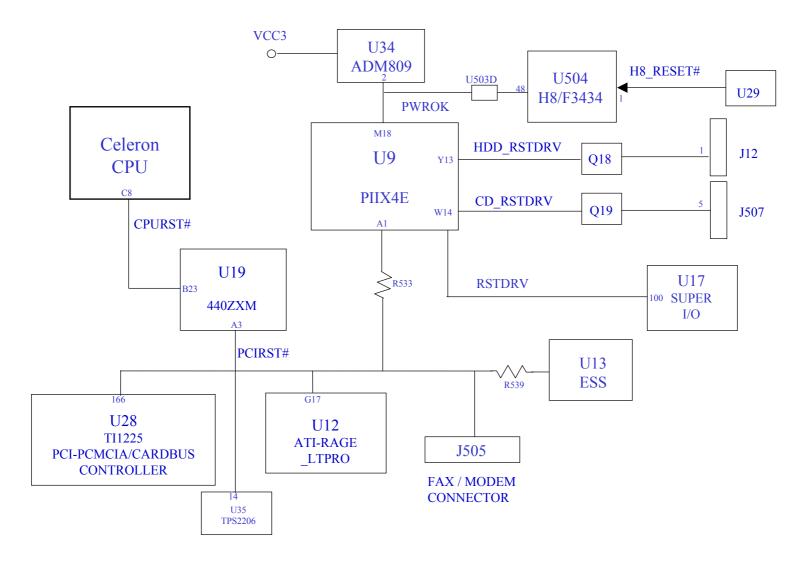

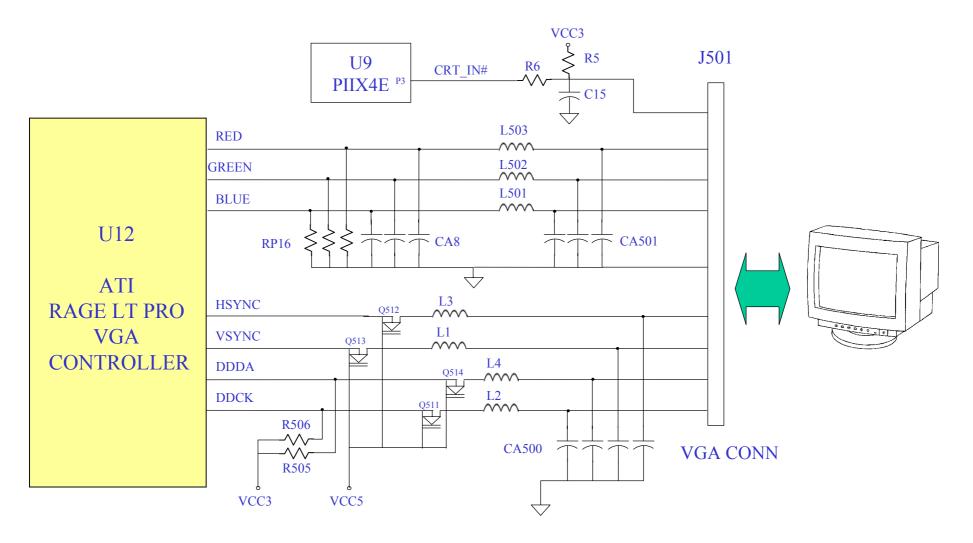

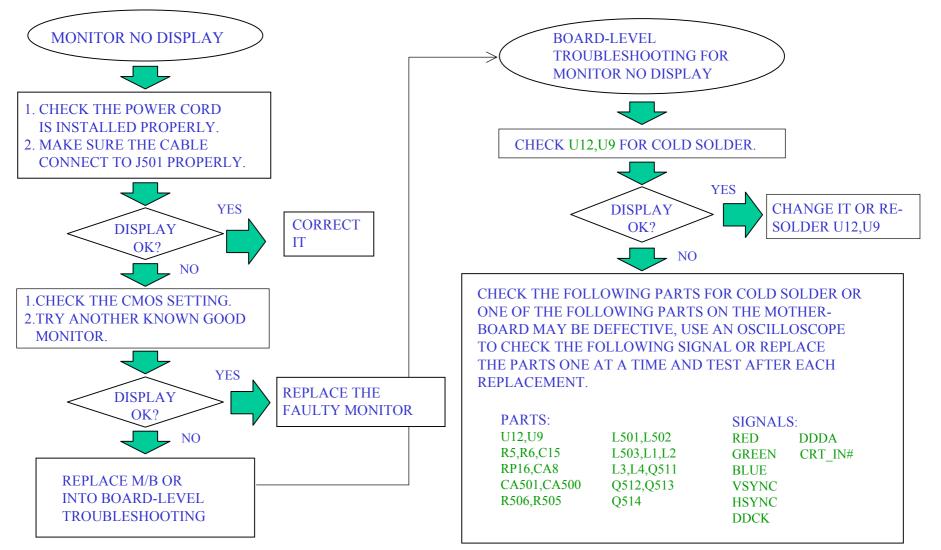

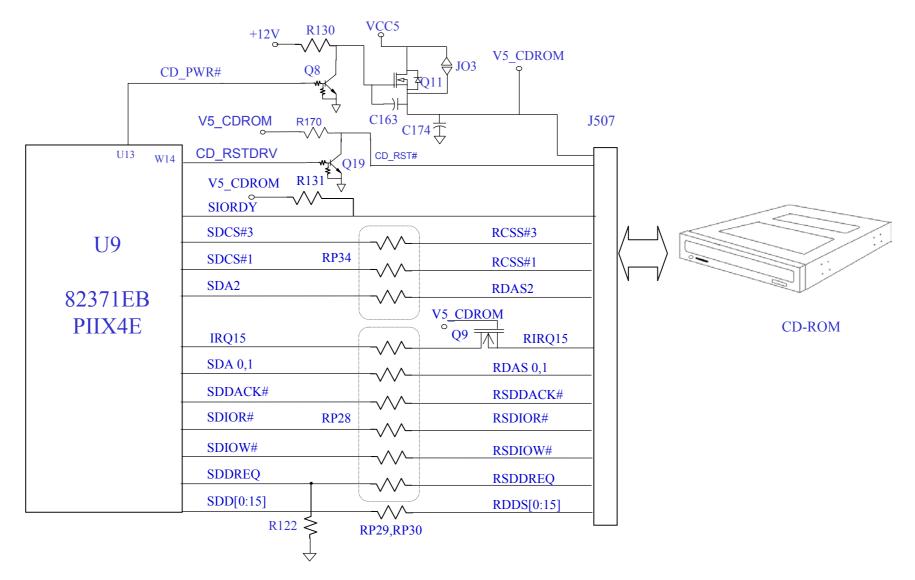

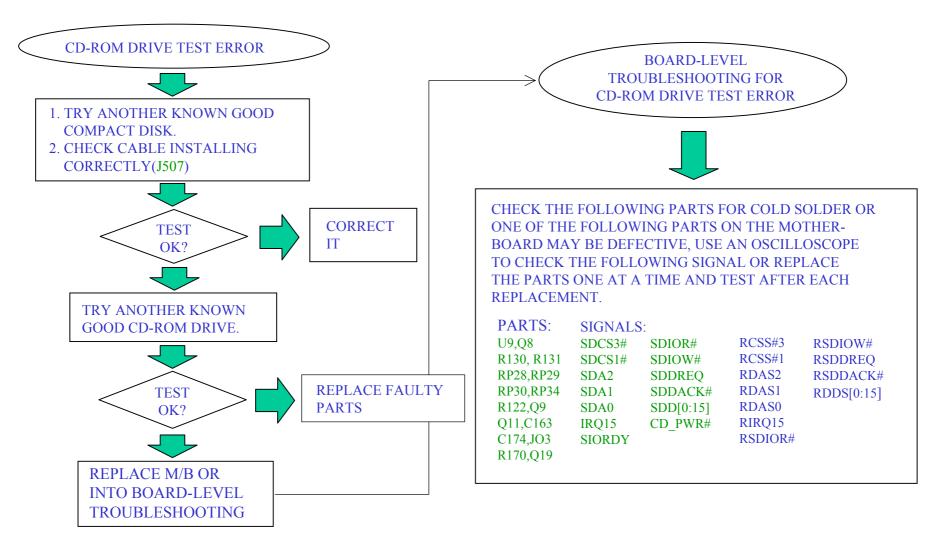

- U9: PIIX4E(82371EB) SOUTH BRIDGE.

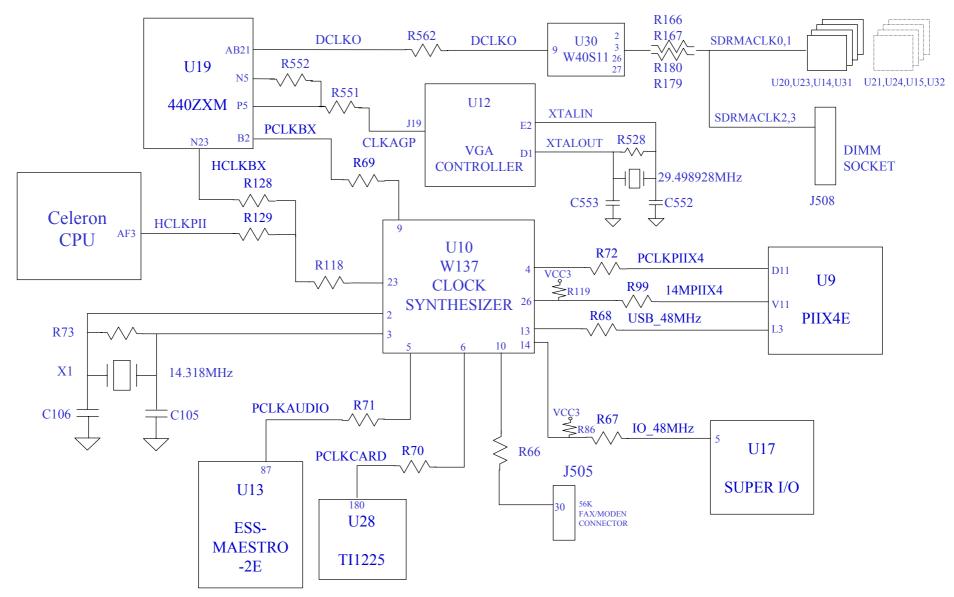

- U10: ICS W137 FREQUENCY SYNTHESIZER.

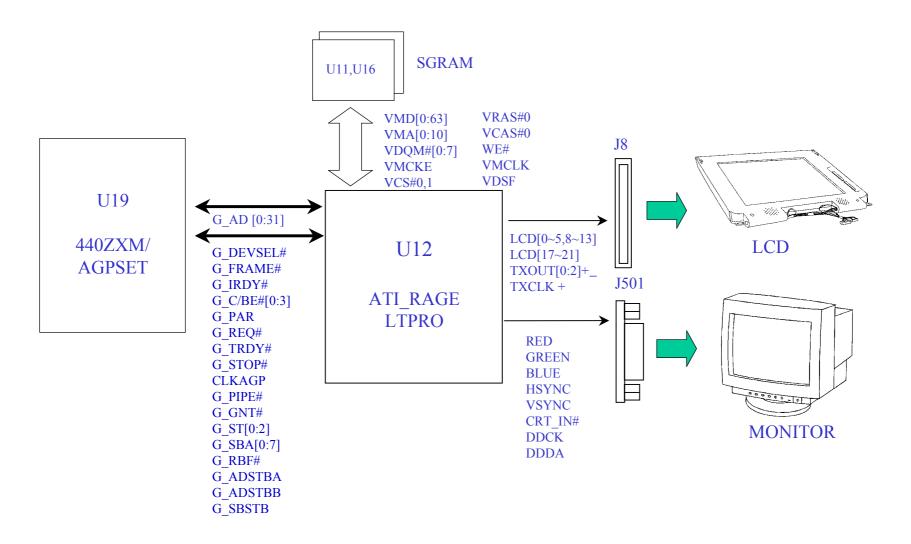

- U11,U16:SGRAM.

- U12:ATI\_RAGE\_LTPRO VGA CTRL.

- U13:ESS-MAESTRO-2E AUDIO CTRL.

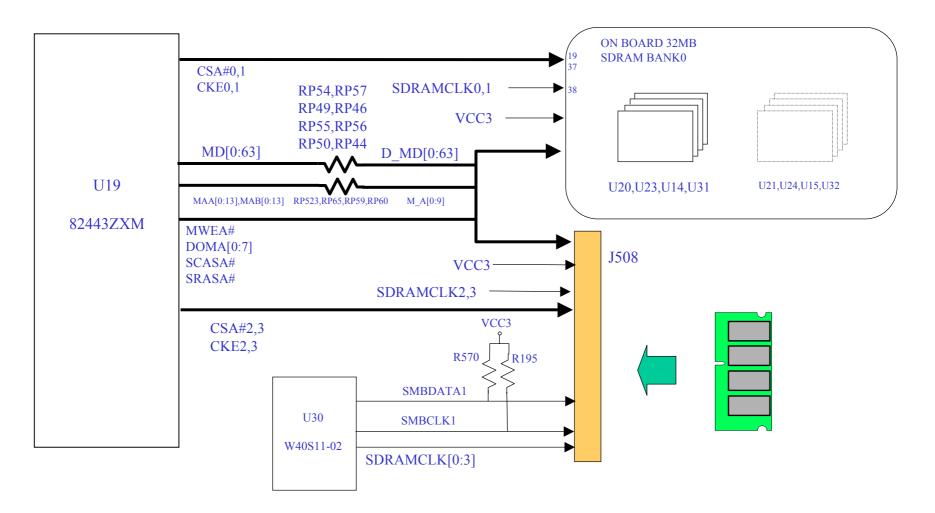

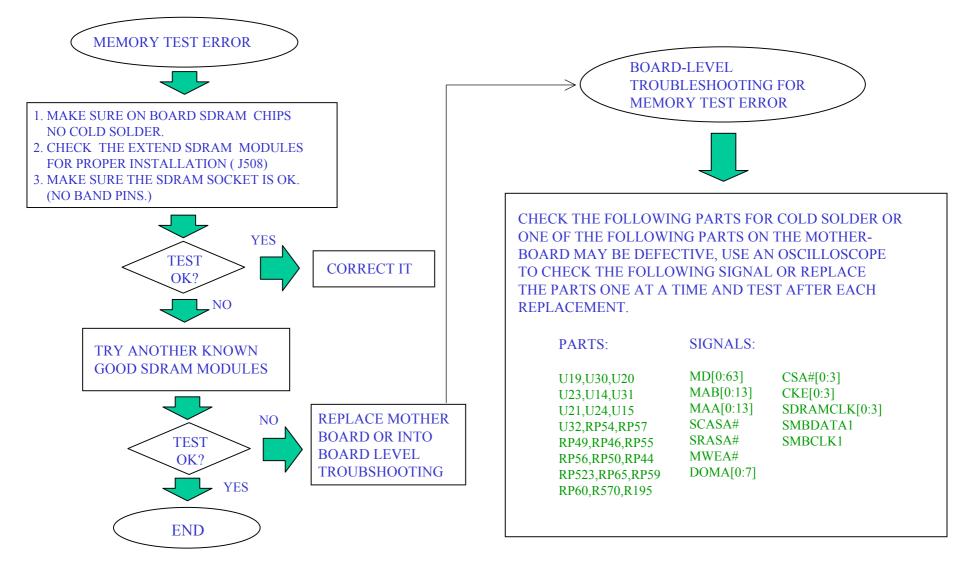

- U14,U20,U23,U31:32MB ON-BOARD MEMORY.

- U17: NS PC93338VJG SUPER I/O CONTROLLER.

- U19: FW82443ZXM HOST BRIDGE CONTROLLER.

- U27: 32P/PLCC/SMT SYSTEM BIOS.

- U28:TI 1225 PCI-PCMCIA/CARDBUS CONTROLLER.

- U30:W40S11-02 CLOCK BUFFER.

## 1. DEFINITION & LOCATION OF CONNECTORS / SWITCHES (A)

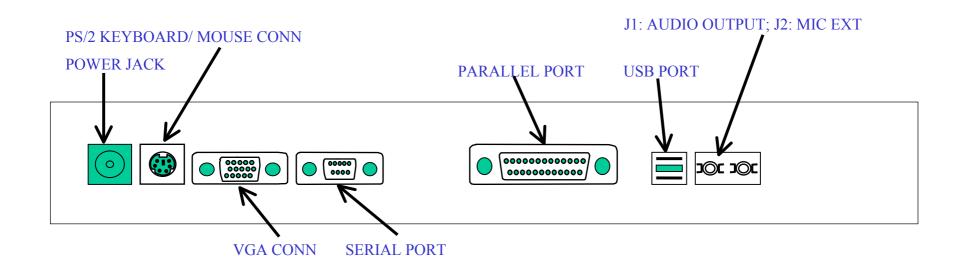

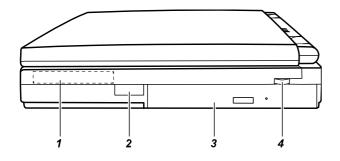

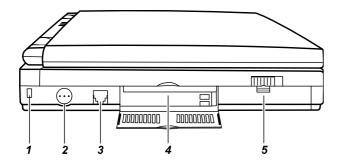

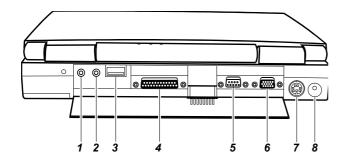

### 2. DEFINITION & LOCATION MAJOR COMPONENTS (SIDE B)

J506: PCMCIA CONNECTOR.

## 2. DEFINITION & LOCATION MAJOR COMPONENTS (SIDE B)

### 3. PIN DESCRIPTIONS OF MAJOR COMPONENTS 3.1 INTEL CELERON PROCESSOR-1

#### Alphabetical Signal Reference (Sheet 1 of 8)

(Sheet 2 of 8)

| Signal    | Туре                                                                                                                                                                                                                                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| A[31:3]#  | I/O                                                                                                                                                                                                                                                 | The A[35:3]# (Address) signals define a 2 36 -byte physical memory address space.<br>When ADS# is active, these pins transmit the address of a transaction; when ADS#<br>is inactive, these pins transmit transaction type information. These signals must<br>connect the appropriate pins of all agents on the Intel ?Celeron?processor system<br>bus. The A[35:24]# signals are parity-protected by the AP1# parity signal, and the<br>A[23:3]# signals are parity-protected by the AP0# parity signal.<br>On the active-to-inactive transition of RESET#, the processors sample the A[35:3]#<br>pins to determine their power-on configuration. See the Pentium II Processor<br>Developer• Manual (Order Number 243502) for details. |  |  |  |

| A20M#     | I                                                                                                                                                                                                                                                   | e A20M# (Address-20 Mask) input signal is asserted, the Intel Celeron<br>essor masks physical address bit 20 (A20#) before looking up a line in any<br>nal cache and before driving a read/write transaction on the bus. Asserting<br>M# emulates the 8086 processor's address wrap-around at the 1 MB boundary.<br>ertion of A20M# is only supported in real mode.<br>M# is an asynchronous signal. However, to ensure recognition of this signal<br>wing an I/O write instruction, it must be valid along with the TRDY# assertion of<br>corresponding I/O Write bus transaction.                                                                                                                                                     |  |  |  |

| ADS#      | I/O                                                                                                                                                                                                                                                 | The ADS# (Address Strobe) signal is asserted to indicate the validity of the transaction address on the A[35:3]# pins. All bus agents observe the ADS# activation to begin parity checking, protocol checking, address decode, internal snoop, or deferred reply ID match operations associated with the new transaction. This signal must connect the appropriate pins on all Intel Celeron processor system bus agents.                                                                                                                                                                                                                                                                                                               |  |  |  |

| BCLK      | I                                                                                                                                                                                                                                                   | The BCLK (Bus Clock) signal determines the bus frequency. All Intel Celeron processor system bus agents must receive this signal to drive their outputs and latch their inputs on the BCLK rising edge.<br>All external timing parameters are specified with respect to the BCLK signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| BNR#      | I/O                                                                                                                                                                                                                                                 | The BNR# (Block Next Request) signal is used to assert a bus stall by any bus agent<br>who is unable to accept new bus transactions. During a bus stall, the current bus<br>owner cannot issue any new transactions.<br>Since multiple agents might need to request a bus stall at the same time, BNR# is a<br>wire-OR signal which must connect the appropriate pins of all Intel Celeron<br>processor system bus agents. In order to avoid wire-OR glitches associated with<br>simultaneous edge transitions driven by multiple drivers, BNR# is activated on<br>specific clock edges and sampled on specific clock edges.                                                                                                            |  |  |  |

| BP[3:2]#  | I/O                                                                                                                                                                                                                                                 | The BP[3:2]# (Breakpoint) signals are outputs from the processor that indicate the status of breakpoints.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| BPM[1:0]# | I/O The BPM[1:0]# (Breakpoint Monitor) signals are breakpoint and performan-<br>monitor signals. They are outputs from the processor which indicate the stat<br>breakpoints and programmable counters used for monitoring processor<br>performance. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| Signal                  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BPRI#                   | Ι    | The BPRI# (Bus Priority Request) signal is used to arbitrate for ownership of the<br>Intel Celeron processor system bus. It must connect the appropriate pins of all Intel<br>Celeron processor system bus agents. Observing BPRI# active (as asserted by the<br>priority agent) causes all other agents to stop issuing new requests, unless such<br>requests are part of an ongoing locked operation. The priority agent keeps BPRI#<br>asserted until all of its requests are completed, then releases the bus by deasserting<br>BPRI#. |

| BSEL                    | I/O  | This signal indicates the host bus frequency supported by the processor. A logic low indicates a host bus frequency of 66 MHz.                                                                                                                                                                                                                                                                                                                                                                                                             |

| BR0#                    | I/O  | The BR0# (Bus Request) pin drives the BREQ[0]# signal in the system. During power-up configuration, the central agent asserts the BREQ0# bus signal in the system to assign the symmetric agent ID to the processor. The processor samples it' s BR0# pin on the active-to-inactive transition of RESET# to obtain it' s symmetric agent ID. The processor asserts BR0# to request the system bus.                                                                                                                                         |

| CPUPRES#<br>(PPGA only) | 0    | The CPUPRES# signal provides the ability for a system board to detect the presence of a processor. This pin is a ground on the processor indicating to the system that a processor is installed.                                                                                                                                                                                                                                                                                                                                           |

| D[63:0]#                | I/O  | The D[63:0]# (Data) signals are the data signals. These signals provide a 64-bit data path between the Intel Celeron processor system bus agents, and must connect the appropriate pins on all such agents. The data driver asserts DRDY# to indicate a valid data transfer.                                                                                                                                                                                                                                                               |

| DBSY#                   | I/O  | The DBSY# (Data Bus Busy) signal is asserted by the agent responsible for driving data on the Intel Celeron processor system bus to indicate that the data bus is in use. The data bus is released after DBSY# is deasserted. This signal must connect the appropriate pins on all Intel Celeron processor system bus agents.                                                                                                                                                                                                              |

| DEFER#                  | I    | The DEFER# signal is asserted by an agent to indicate that a transaction cannot be glaranteed in-order completion. Assertion of DEFER# is normally the responsibility of the addressed memory or I/O agent. This signal must connect the appropriate pns of all Intel Celeron processor system bus agents.                                                                                                                                                                                                                                 |

| DRDY#                   | I/O  | The DRDY# (Data Ready) signal is asserted by the data driver on each data transfer, indicating valid data on the data bus. In a multicycle data transfer, DRDY# may be deasserted to insert idle clocks. This signal must connect the appropriate pins of all Intel Celeron processor system bus agents.                                                                                                                                                                                                                                   |

| EDGCTRL                 | Ι    | The EDGCTRL input provides GTL+ edge control and should be pulled up to VCC CORE with a 51 $\Omega$ ?% resistor.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| EMI<br>(S.E.P.P. only)  | I    | EMI pins should be connected to motherboard ground and/or to chassis ground through zero ohm $(0\Omega)$ resistors. The zero ohm resistors should be placed in close proximity to the Intel Celeron processor connector. The path to chassis ground should be short in length and have a low impedance. These pins are used for EMI                                                                                                                                                                                                        |

management purposes.

### **3.1 INTEL CELERON PROCESSOR-2**

#### Alphabetical Signal Reference (Sheet 3 of 8)

| Signal      | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FERR#       | 0    | The FERR# (Floating-point Error) signal is asserted when the processor detects an unmasked floating-point error. FERR# is similar to the ERROR# signal on the Intel 387 coprocessor, and is included for compatibility with systems using MS-DOS*-type floating-point error reporting.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| FLUSH#      | Ι    | When the FLUSH# input signal is asserted, the processor writes back all data in the<br>Modified state from the internal cache and invalidates all internal cache lines. At the<br>completion of this operation, the processor issues a Flush Acknowledge transaction.<br>The processor does not cache any new data while the FLUSH# signal remains<br>asserted.<br>FLUSH# is an asynchronous signal. However, to ensure recognition of this signal<br>following an I/O write instruction, it must be valid along with the TRDY# assertion of<br>the corresponding I/O Write bus transaction.<br>On the active-to-inactive transition of RESET#, the processor samples FLUSH# to<br>determine its power-on configuration. See Pentium Pro Family Developer• Manual,<br>Volume 1: Specifications (Order Number 242690) for details. |

| HIT#, HITM# | I/O  | The HIT# (Snoop Hit) and HITM# (Hit Modified) signals convey transaction snoop<br>operation results, and must connect the appropriate pins of all Intel Celeron<br>processor system bus agents. Any such agent may assert both HIT# and HITM#<br>together to indicate that it requires a snoop stall, which can be continued by<br>reasserting HIT# and HITM# together.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| IERR#       | 0    | The IERR# (Internal Error) signal is asserted by a processor as the result of an internal error. Assertion of IERR# is usually accompanied by a SHUTDOWN transaction on the Intel Celeron processor system bus. This transaction may optionally be converted to an external error signal (e.g., NMI) by system core logic. The processor will keep IERR# asserted until the assertion of RESET#, BINIT#, or INIT#.                                                                                                                                                                                                                                                                                                                                                                                                                |

| IGNNE#      | Ι    | The IGNNE# (Ignore Numeric Error) signal is asserted to force the processor to<br>ignore a numeric error and continue to execute noncontrol floating-point instructions.<br>If IGNNE# is deasserted, the processor generates an exception on a noncontrol<br>foating-point instruction if a previous floating-point instruction caused an error.<br>IGNNE# has no effect when the NE bit in control register 0 is set.<br>IGNNE# is an asynchronous signal. However, to ensure recognition of this signal<br>following an I/O write instruction, it must be valid along with the TRDY# assertion of<br>the corresponding I/O Write bus transaction.                                                                                                                                                                               |

| INIT#       | I    | The INIT# (Initialization) signal, when asserted, resets integer registers inside all processors without affecting their internal (L1) caches or floating-point registers. Each processor then begins execution at the power-on Reset vector configured during power-on configuration. The processor continues to handle snoop requests during INIT# assertion. INIT# is an asynchronous signal and must connect the appropriate pins of all bus agents. If INIT# is sampled active on the active to inactive transition of RESET#, then the processor executes its Built-in Self-Test (BIST).                                                                                                                                                                                                                                    |

#### (Sheet 4 of 8)

| Signal                    | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LINT[1:0]                 | I    | The LINT[1:0] (Local APIC Interrupt) signals must connect the appropriate pins of all APIC Bus agents, including all processors and the core logic or I/O APIC component. When the APIC is disabled, the LINT0 signal becomes INTR, a maskable interrupt request signal, and LINT1 becomes NMI, a nonmaskable interrupt. INTR and NMI are backward compatible with the signals of those names on the Pentium ?processor. Both signals are asynchronous. Both of these signals must be software configured via BIOS programming of the APIC register space to be used either as NMI/INTR or LINT[1:0]. Because the APIC is enabled by default after Reset, operation of these pins as LINT[1:0] is the default configuration. |

| LOCK#                     | I/O  | The LOCK# signal indicates to the system that a transaction must occur atomically.<br>This signal must connect the appropriate pins of all system bus agents. For a locked<br>sequence of transactions, LOCK# is asserted from the beginning of the first<br>transaction end of the last transaction.<br>When the priority agent asserts BPRI# to arbitrate for ownership of the system bus,<br>it will wait until it observes LOCK# deasserted. This enables symmetric agents to<br>retain ownership of the system bus throughout the bus locked operation and ensure<br>the atomicity of lock.                                                                                                                             |

| PICCLK                    | I    | The PICCLK (APIC Clock) signal is an input clock to the processor and core logic or I/O APIC which is required for operation of all processors, core logic, and I/O APIC components on the APIC bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| PICD[1:0]                 | I/O  | The PICD[1:0] (APIC Data) signals are used for bidirectional serial message passing on the APIC bus, and must connect the appropriate pins of the Intel Celeron processor for proper initialization.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| PLL1, PLL2<br>(PPGA only) | I    | All Intel Celeron processors have internal analog PLL clock generators that require quiet power supplies. PLL1 and PLL2 are inputs to the internal PLL and should be connected to VCC CORE through a low-pass filter that minimizes jitter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| PRDY#                     | 0    | The PRDY (Probe Ready) signal is a processor output used by debug tools to determine processor debug readiness.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| PREQ#                     | I    | The PREQ# (Probe Request) signal is used by debug tools to request debug operation of the processors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| REQ[4:0]#                 | I/O  | The REQ[4:0]# (Request Command) signals must connect the appropriate pins of all processor system bus agents. They are asserted by the current bus owner over two clock cycles to define the currently active transaction type.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| RS[2:0]#                  | I    | The RS[2:0]# (Response Status) signals are driven by the response agent (the agent responsible for completion of the current transaction), and must connect the appropriate pins of all processor system bus agents.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

### **3.1 INTEL CELERON PROCESSOR-3**

#### Alphabetical Signal Reference (Sheet 5 of 8)

| Signal  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PWRGOOD | I    | The PWRGOOD (Power Good) signal is a 2.5 V tolerant processor input. The processor requires this signal to be a clean indication that the clocks and power supplies (VCC CORE, etc.) are stable and within their specifications. Clean implies that the signal will remain low (capable of sinking leakage current), without glitches, from the time that the power supplies are turned on until they come within specification. The signal must then transition monotonically to a high (2.5 V) state. Figure 23 illustrates the relationship of PWRGOOD to other system signals. PWRGOOD can be driven inactive at any time, but clocks and power must again be stable before a subsequent rising edge of PWRGOOD. It must also meet the minimum pulse width specification in Table 14 and Table 15, and be followed by a 1 ms RESET# pulse. The PWRGOOD signal must be supplied to the processor; it is used to protect internal circuits against voltage sequencing issues. It should be driven high throughout boundary scan operation. <b>PWRGOOD Relationship at Power-On</b> BCLK VCC core , V REF PWRGOOD RESET#                                                                           |  |

| RESET#  | I    | Asserting the RESET# signal resets the processor to a known state and invalidates<br>the L1 cache without writing back any of the contents. RESET# must remain active<br>for one microsecond for a • arm?Reset; for a power-on Reset, RESET# must stay<br>active for at least one millisecond after VCC CORE and CLK have reached their proper<br>specifications. On observing active RESET#, all system bus agents will deassert<br>their outputs within two clocks.<br>A number of bus signals are sampled at the active-to-inactive transition of RESET#<br>for power-on configuration. These configuration options are described in the<br>Pentium Pro Family Developer• Manual, Volume 1: Specifications (Order Number<br>42690).<br>The processor may have its outputs tristated via power-on configuration. Otherwise,<br>if INIT# is sampled active during the active-to-inactive transition of RESET#, the<br>processor will execute its Built-in Self-Test (BIST). Whether or not BIST is executed,<br>the processor will begin program execution at the power on Reset vector (default<br>0_FFFF_FFF0h). RESET# must connect the appropriate pins of all processor<br>system bus agents. |  |

| SMI#    | I    | System bus agents.<br>The SMI# (System Management Interrupt) signal is asserted asynchronously by<br>system logic. On accepting a System Management Interrupt, processors save the<br>qurrent state and enter System Management Mode (SMM). An SMI Acknowledge<br>transaction is issued, and the processor begins program execution from the SMM<br>handler.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

#### (Sheet 6 of 8)

| Signal                      | Туре |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |                                                             |   |

|-----------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------------------------------------------------------|---|

| SLOTOCC#<br>(S.E.P.P. only) | 0    | SLOTOCC# is defined to allow a system design to detect the presence of a terminator card or processor in a SC242 connector. This pin is not a signal; rather, it is a short to VSS. Combined with the VID combination of VID[4:0]= 11111 (see Section 2.5), a system can determine if a SC242 connector is occupied, and whether a processor core is present. The states and values for determining the type of cartridge in the SC242 connector is shown below.                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |                                                             |   |

|                             |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SC242 Occupation Truth T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | able     | St. 1                                                       | _ |

|                             |      | Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          | Status                                                      |   |

|                             |      | SLOTOCC#<br>VID[4:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0<br>Anything other than ?1111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          | essor with core in SC242<br>ector.                          |   |

|                             |      | SLOTOCC#<br>VID[4:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0<br>11111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          | ninator cartridge in SC242<br>ector (i.e., no core<br>ent). |   |

|                             |      | SLOTOCC#<br>VID[4:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | l<br>Any value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SC2      | 42 connector not occupied.                                  |   |

| SLP#                        | I    | The SLP# (Sleep) signal, when asserted in Stop-Grant state, causes processors to enter the Sleep state. During Sleep state, the processor stops providing internal clock signals to all units, leaving only the Phase-Locked Loop (PLL) still operating. Processors in this state will not recognize snoops or interrupts. The processor will recognize only assertions of the SLP#, STPCLK#, and RESET# signals while in Sleep state. If SLP# is deasserted, the processor exits Sleep state and returns to Stop-Grant state, restarting its internal clock signals to the bus and APIC processor core units. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |                                                             |   |

| STPCLK#                     | Ι    | low power Stop-C<br>transaction, and st<br>except the bus and<br>and service intern<br>processor restarts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | The STPCLK# (Stop Clock) signal, when asserted, causes processors to enter a low power Stop-Grant state. The processor issues a Stop-Grant Acknowledge transaction, and stops providing internal clock signals to all processor core units except the bus and APIC units. The processor continues to snoop bus transactions and service interrupts while in Stop-Grant state. When STPCLK# is deasserted, the processor restarts its internal clock to all units and resumes execution. The assertion of STPCLK# has no effect on the bus clock; STPCLK# is an asynchronous input. |          |                                                             |   |

| ТСК                         | Ι    | The TCK (Test C<br>Test Access Port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | The TCK (Test Clock) signal provides the clock input for the Intel Celeron processor<br>Test Access Port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |                                                             |   |

| TDI                         | Ι    | The TDI (Test Data In) signal transfers serial test data into the processor. TDI provides the serial input needed for JTAG specification support.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |                                                             |   |

|                             |      | provides the serial                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | I input needed for JTAG spec                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ificatio | on support.                                                 |   |

### **3.1 INTEL CELERON PROCESSOR-4**

#### Alphabetical Signal Reference (Sheet 7 of 8)

| Signal                    | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|---------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| TESTHI<br>(S.E.P.P. only) | I    | Refer to Section 2.6 for implementation details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| THERMDN                   | 0    | Ihermal Diode p-n junction. Used to calculate core temperature. See Section 4.1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| THERMDP                   | Ι    | Thermal Diode p-n junction. Used to calculate core temperature. See Section 4.1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| THERMTRIP#                | 0    | he processor protects itself from catastrophic overheating by use of an internal<br>nermal sensor. This sensor is set well above the normal operating temperature to<br>usure that there are no false trips. The processor will stop all execution when the<br>nction temperature exceeds approximately 135 • . This is signaled to the system<br>/ the THERMTRIP# (Thermal Trip) pin. Once activated, the signal remains latched,<br>id the processor stopped, until RESET# goes active. There is no hysteresis built<br>to the thermal sensor itself, as long as the die temperature drops below the trip<br>vel, a RESET# pulse will reset the processor and execution will continue. If the<br>mperature has not dropped below the trip level, the processor will reassert<br>HERMTRIP# and remain stopped. |  |  |  |  |  |

| TMS                       | I    | The TMS (Test Mode Select) signal is a JTAG specification support signal used by debug tools.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| TRDY#                     | Ι    | The TRDY# (Target Ready) signal is asserted by the target to indicate that it is ready to receive a write or implicit writeback data transfer. TRDY# must connect the appropriate pins of all system bus agents.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| TRST#                     | I    | The TRST# (Test Reset) signal resets the Test Access Port (TAP) logic. Intel Celeron processors require this signal to be driven low during power on Reset. A 680 ohm resistor is the suggested value for a pull down resistor on TRST#.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| VCC 1.5<br>(PPGA only)    | I    | The VCC CMOS pin provides the CMOS voltage for use by the platform. The 2.5V must be provided to the VCC 2.5 input and 1.5V must be provided to the VCC 1.5 input. The processor re-routes the 2.5V input to the VCC CMOS output via the package. Future processors requiring 1.5V CMOS voltage levels will route the 1.5V at the VCC 1.5 input to the VCC CMOS output.                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| VCC 2.5<br>(PPGA only)    | I    | The VCC CMOS pin provides the CMOS voltage for use by the platform. The 2.5V must be provided to the VCC 2.5 input and 1.5V must be provided to the VCC 1.5 input. The processor re-routes the 2.5V input to the VCC CMOS output via the package. Future processors requiring 1.5V CMOS voltage levels will route the 1.5V at the VCC 1.5 input to the VCC CMOS output.                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| VCC CMOS<br>(PPGA only)   | 0    | The VCC CMOS pin provides the CMOS voltage for use by the platform. The 2.5V must be provided to the VCC 2.5 input and 1.5V must be provided to the VCC 1.5 input. The processor re-routes the 2.5V input to the VCC CMOS output via the package. Future processors requiring 1.5V CMOS voltage levels will route the 1.5V at the VCC 1.5 input to the VCC CMOS output.                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

#### (Sheet 8 of 8)

| Signal                                       | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCORE DET<br>(PPGA only)                     | 0    | The VCORE DET signal will float for 2.0 V core processors and will be grounded for future processors with a lower core voltage.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| VID[4:0]<br>(S.E.P.P.)<br>VID[3:0]<br>(PPGA) | 0    | The VID (Voltage ID) pins can be used to support automatic selection of power<br>supply voltages. These pins are not signals, but are either an open circuit or a short<br>circuit to VSS on the processor. The combination of opens and shorts defines the<br>voltage required by the processor. The VID pins are needed to cleanly support<br>voltage specification variations on Intel Celeron processors. See Table 1 for<br>definitions of these pins. The power supply must supply the voltage that is requested<br>by these pins, or disable itself. |

| V REF [7:0]<br>(PPGA only)                   | Ι    | These input signals are used by the GTL+ inputs as a reference voltage. GTL+ inputs are differential receivers and will use this voltage to determine whether the signal is a logic high or logic low.                                                                                                                                                                                                                                                                                                                                                      |

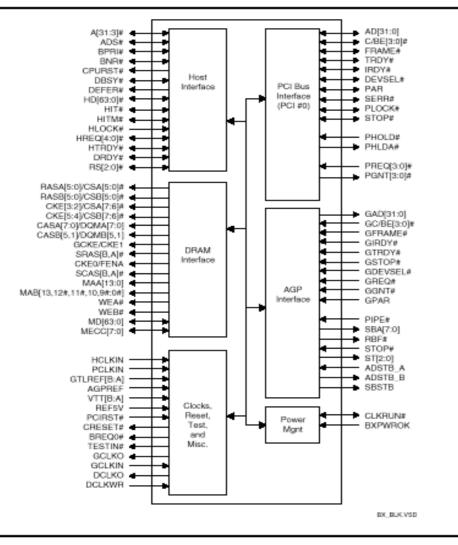

### **3.2 INTEL 82443ZXM HOST BRIDGE CONTROLLER-1**

#### •Intel 82443ZX Features:

- · Processor/host bus support

- Optimized for Pentium<sup>®</sup> II processor at 100 MHz system bus frequency; Support for 66 MHz

- In-order transaction and dynamic deferred transaction support

- Desktop optimized GTL+ bus driver technology (gated GTL+ receivers for reduced power)

- · Integrated DRAM controller

- 8 to 256Mbytes

- Supports 2 double-sided DIMMs (4 rows memory)

- 64-bit data interface

- Unbuffered SDRAM (Synchronous) DRAM Support (x-1-1-1 access @ 66 MHz, x-1-1-1 access @ 100 MHz)

- Enhanced SDRAM Open Page Architecture Support for 16- and 64-Mbit DRAM devices with 2k, 4k and 8k page sizes

- · PCI bus interface

- PCI Rev. 2.1, 3.3V and 5V, 33MHz interface compliant

- PCI Parity Generation Support

- Data streaming support from PCI to DRAM

- Delayed Transaction support for PCI-DRAM Reads

- Supports concurrent CPU, AGP and PCI transactions to main memory

- AGP interface

- Supports single AGP compliant device (AGP-66/133 3.3V device)

- AGP Specification Rev 1.0 compliant

- AGP-data/transaction flow optimized arbitration mechanism

- AGP side-band interface for efficient request pipelining without interfering with the data streams

- AGP-specific data buffering

- Supports concurrent CPU, AGP and PCI transactions to main memory

- AGP high-priority transactions ("expedite") support

- · Power Management Functions

- Stop Clock Grant and Halt special cycle translation (host to PCI Bus)

- Dynamic power down of idle DRAM rows

- Independent, internal dynamic clock gating reduces average power dissipationt

- Packaging/Voltage

- 492 Pin BGA

- 3.3V core and mixed 3.3V and GTL I/O

- · Supporting I/O Bridge

- System Management Bus (SMB) with support for DIMM Serial Presence Detect (SPD)

- PCI-ISA Bridge (PIIX4E)

- 3.3V core and mixed 5V, 3.3V I/O and interface to the 2.5V CPU signals via open-drain output buffers

### 3.2 INTEL 82443ZXM HOST BRIDGE CONTROLLER-2

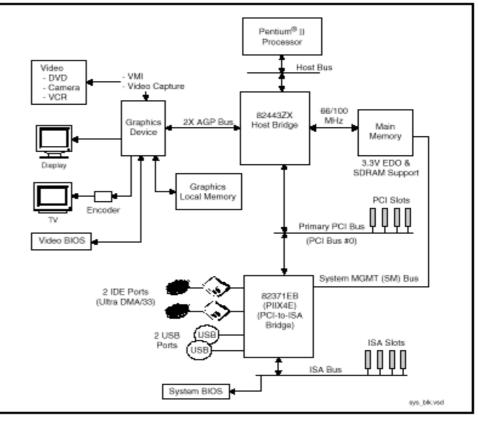

#### •Intel 82443ZX Simplified Block Diagram:

#### •Intel 440ZX AGPset System Block Diagram:

11

### **3.2 INTEL 82443ZXM HOST BRIDGE CONTROLLER-3**

#### Table 3.2.1. Host Interface Signals (Sheet 1 of 2)

| Name       | Туре | Description                                                                               |

|------------|------|-------------------------------------------------------------------------------------------|

| CPURST#    | 0    | <b>CPU Reset.</b> The CPURST# pin is an output from the 82443ZX. The 82443ZX              |

|            | GTL+ | generates this signal based on the PCIRST# input (from PIIX4E) and also the               |

|            |      | SUSTAT# pin in mobile mode. The CPURST# allows the CPUs to begin execution                |

|            |      | in a known state.                                                                         |

| A[31:3]#   | I/O  | Address Bus: A[31:3]# connect to the CPU address bus. During CPU cycles, the              |

|            | GTL+ | A[31:3]# are inputs.                                                                      |

| HD[63:0]#  | I/O  | Host Data: These signals are connected to the CPU data bus. Note that the data            |

|            | GTL+ | signals are inverted on the CPU bus.                                                      |

| ADS#       | I/O  | Address Strobe: The CPU bus owner asserts ADS# to indicate the first of two               |

|            | GTL+ | cycles of a request phase.                                                                |

| BNR#       | I/O  | Block Next Request: Used to block the current request bus owner from issuing a            |

|            | GTL+ | new request. This signal is used to dynamically control the CPU bus pipeline depth.       |

| BPRI#      | 0    | Priority Agent Bus Request: The 82443ZX is the only Priority Agent on the CPU             |

|            | GTL+ | bus. It asserts this signal to obtain the ownership of the address bus. This signal has   |

|            |      | priority over symmetric bus requests and will cause the current symmetric owner to        |

|            |      | stop issuing new transactions unless the HLOCK# signal was asserted.                      |

| BREQ0#     | 0    | Symmetric Agent Bus Request: Asserted by the 82443ZX when CPURST# is                      |

|            | GTL+ | asserted to configure the symmetric bus agents. BREQ0# is negated 2 host clocks           |

|            |      | after CPURST# is negated.                                                                 |

| DBSY#      | I/O  | Data Bus Busy: Used by the data bus owner to hold the data bus for transfers              |

|            | GTL+ | requiring more than one cycle.                                                            |

| DEFER#     | 0    | Defer: The 82443ZX generates a deferred response as defined by the rules of the           |

|            | GTL+ | 82443ZX? dynamic defer policy. The 82443ZX also uses the DEFER# signal to                 |

|            |      | indicate a CPU retry response.                                                            |

| DRDY#      | I/O  | Data Ready: Asserted for each cycle that data is transferred.                             |

|            | GTL+ |                                                                                           |

| HIT#       | I/O  | Hit: Indicates that a caching agent holds an unmodified version of the requested          |

|            | GTL+ | line. Also driven in conjunction with HITM# by the target to extend the snoop             |

|            |      | window.                                                                                   |

| HITM#      | I/O  | Hit Modified: Indicates that a caching agent holds a modified version of the              |

|            | GTL+ | requested line and that this agent assumes responsibility for providing the line. Also    |

|            |      | driven in conjunction with HIT# to extend the snoop window.                               |

| HLOCK#     | Ι    | Host Lock: All CPU bus cycles sampled with the assertion of HLOCK# and                    |

|            | GTL+ | ADS#, until the negation of HLOCK# must be atomic, i.e. no PCI or AGP                     |

|            |      | snoopable access to DRAM is allowed when HLOCK# is asserted by the CPU.                   |

| HREQ[4:0]# | I/O  | Request Command: Asserted during both clocks of request phase. In the first               |

|            | GTL+ | clock, the signals define the transaction type to a level of detail that is sufficient to |

|            |      | begin a snoop request. In the second clock, the signals carry additional information      |

|            |      | to define the complete transaction type. The transactions supported by the 82443ZX        |

|            |      | Host Bridge are defined in the Host Interface section of this document.                   |

| HTRDY#     | I/O  | Host Target Ready: Indicates that the target of the CPU transaction is able to enter      |

|            | GTL+ | the data transfer phase.                                                                  |

#### Table 3.2.1. Host Interface Signals (Sheet 2 of 2)

| Name     | Туре | Description           |                                                                             |  |

|----------|------|-----------------------|-----------------------------------------------------------------------------|--|

| RS[2:0]# | I/O  | <b>Response Signa</b> | <b>Is:</b> Indicates type of response according to the following the table: |  |

|          | GTL+ | RS[2:0] Res           | sponse type                                                                 |  |

|          |      | 000                   | Idle state                                                                  |  |

|          |      | 001                   | Retry response                                                              |  |

|          |      | 010                   | Deferred response                                                           |  |

|          |      | 011                   | Reserved (not driven by 82443ZX)                                            |  |

|          |      | 100                   | Hard Failure (not driven by 82443ZX)                                        |  |

|          |      | 101                   | No data response                                                            |  |

|          |      | 110                   | Implicit Writeback                                                          |  |

|          |      | 111                   | Normal data response                                                        |  |

#### Table 3.2.2. Host Signals Not supported by the 82443ZX

| Signal    | Function                  | Not Supported By 82443ZX                                            |

|-----------|---------------------------|---------------------------------------------------------------------|

| A[35:32]# | Address                   | Extended addressing (over 4 GB)                                     |

| AERR#     | Address Parity            | Parity protection on address bus                                    |

|           | Error                     |                                                                     |

| AP[1:0]#  | Address Parity            | Parity protection on address bus                                    |

| BINIT#    | <b>Bus Initialization</b> | Checking for bus protocol violation and protocol recovery mechanism |

| DEP[7:0]# | Data Bus                  | Enhanced data bus integrity                                         |

|           | ECC/Parity                |                                                                     |

| IERR#     | Internal Error            | Direct internal error observation via IERR# pin                     |

| INIT#     | Soft Reset                | Implemented by PIIX4E, BIST supported by external logic.            |

| BERR#     | Bus Error                 | Unrecoverable error without a bus protocol violation                |

| RP#       | Request Parity            | Parity protection on ADS# and PREQ[4:0]#                            |

| RSP#      | Response Parity           | Parity protection on RS[2:0]#                                       |

|           | Signal                    |                                                                     |

#### Table 3.2.3. DRAM Interface Signals (Sheet 1 of 2)