# **TROUBLE SHOOTING GUIDE FOR NOTEBOOK** 5023

## BY:

### **GEORGE FENG**

# **TECHNICAL SUPPORT & SERVICE CENTER**

| 1. | DEFINITION OF CONNECTORS  |       |

|----|---------------------------|-------|

|    | & SWITCHES                | 4     |

| 2. | LOCATION OF SWITCHES &    |       |

|    | CONNECTORS                | 5     |

| 3. | MAJOR COMPONENTS          | 6     |

| 4. | LOCATION OF MAJOR         |       |

|    | COMPONENTS                | 7     |

| 5. | PIN DESCRIPTIONS OF MAJOR |       |

|    | CHIPS                     | 8~18  |

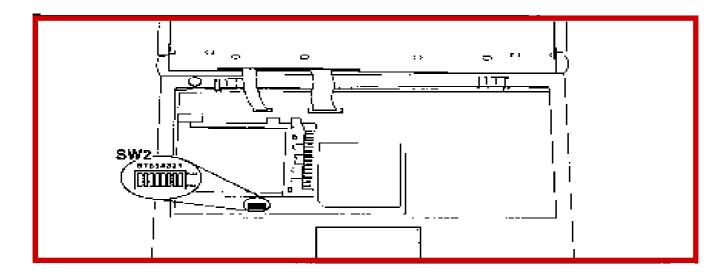

| 6. | SWITCHES SETTING          | 19    |

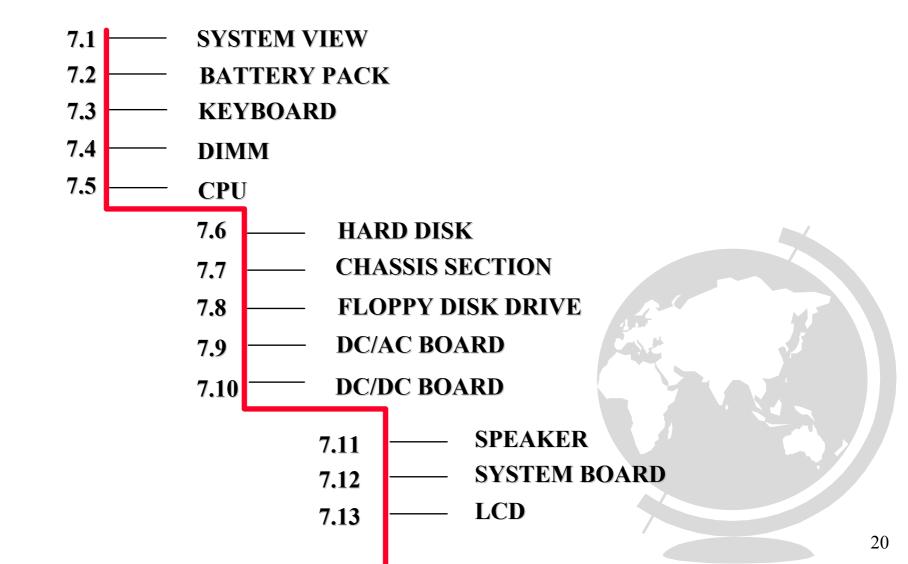

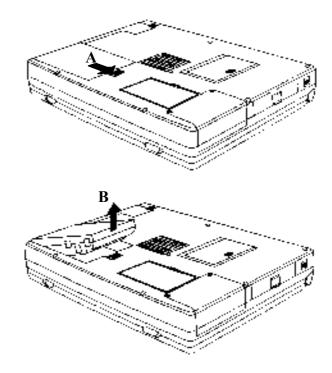

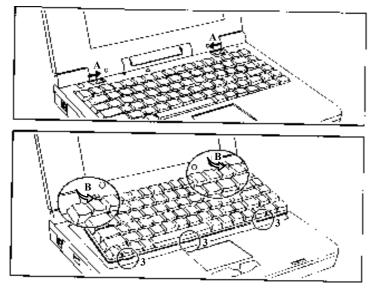

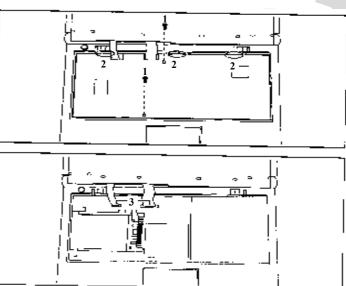

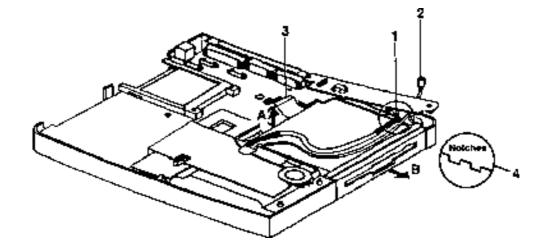

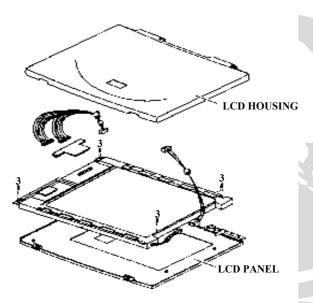

| 7. | ASSEMBLY & DISASSEMBLY    | 20~33 |

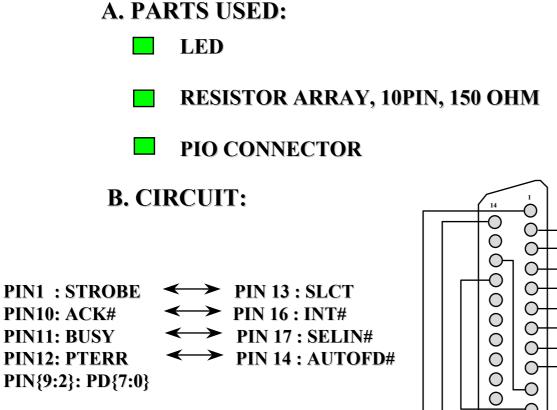

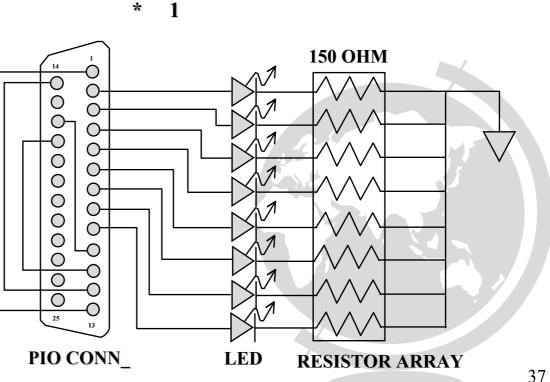

| 8. | MAINTENANCE DIAGNOSTICS   | 34~37 |

| 9. | TROUBLE SHOOTING                       | 38~70  |

|----|----------------------------------------|--------|

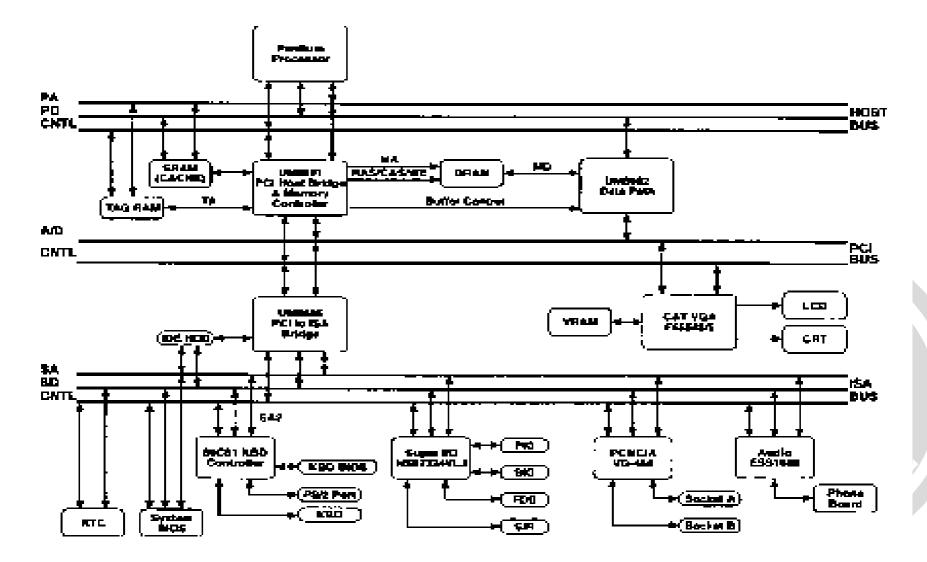

| 10 | . SYSTEM BLOCK DIAGRAM &<br>SCHEMATICS | 71~95  |

| 11 | . EXPLODED VIEWS                       | 96~98  |

| 12 | . SPARE PARTS LIST                     | 99~106 |

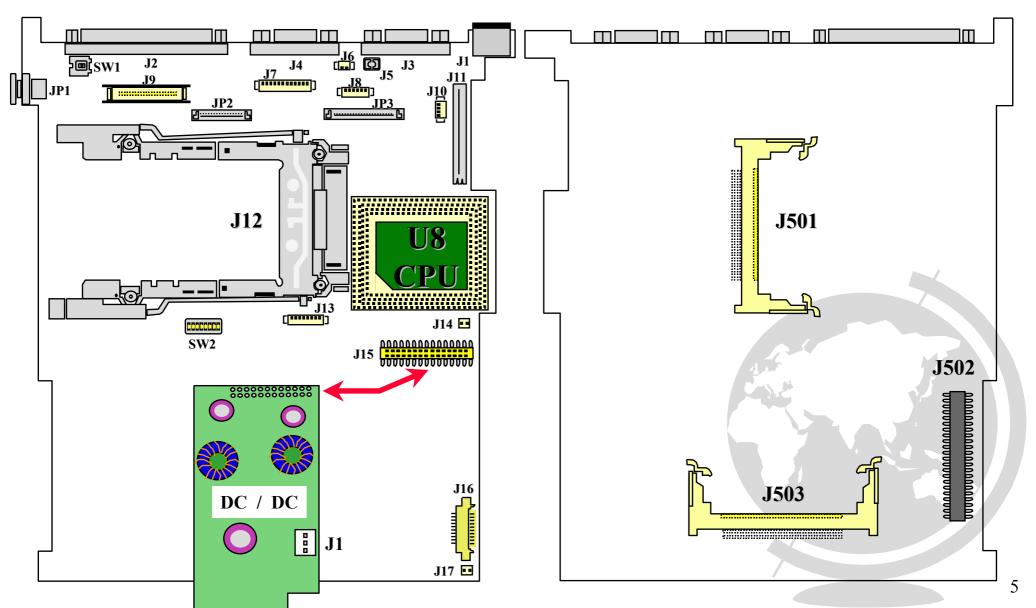

## **1. DEFINITION OF CONNECTORS & SWITCHES**

| J1 : PS/2 KEYBOARD & MOUSE CONNECTOR | J14 : SPEAKER CONNECTOR                |

|--------------------------------------|----------------------------------------|

| J2 : PARALLEL PORT(PIO)              | J15 : DC/DC TO BOARD CONNECTOR         |

| J3 : SERIAL PORT (SIO)               | J16 : AUDIO BOARD CONNECTOR            |

| J4 : CRT VIDEO CONNECTOR             | J17 : MICROPHONE CONNECTOR             |

| J5 : SUSPEND / RESUME BUTTON         | J501, J503 : MEMORY MODULE CONNECTOR   |

| J6 : COVER SWITCH                    | J502 : HARD DISK CONNECTOR             |

| J7 : ICON LCD MODULE CONNECTOR       | JP1 : POWER JACK                       |

| J8 : BACKLIGHT CONNECTOR             | JP2, JP3 : INTERNAL KEYBOARD CONNECTOR |

| J9 : LCD MODULE CONNECTOR            | SW1 : POWER BUTTON                     |

| J10: SIR PORT                        |                                        |

| J11: FLOPPY DRIVE CONNECTOR          | DC /DC BOARD                           |

| J12: PCMCIA IC CARD CONNECTOR        |                                        |

| J13 : TOUCHPAD CONNECTOR             | J1 : BATTERY CONNECTOR                 |

|                                      |                                        |

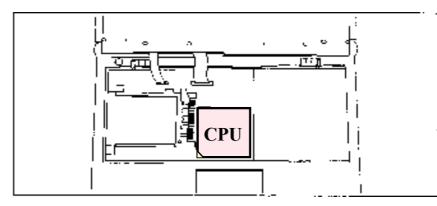

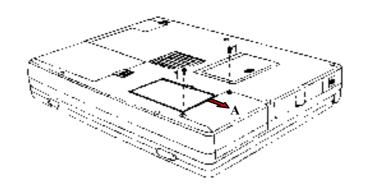

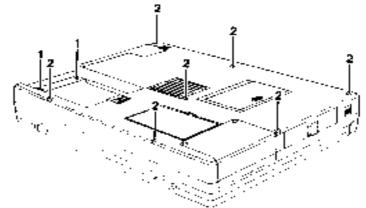

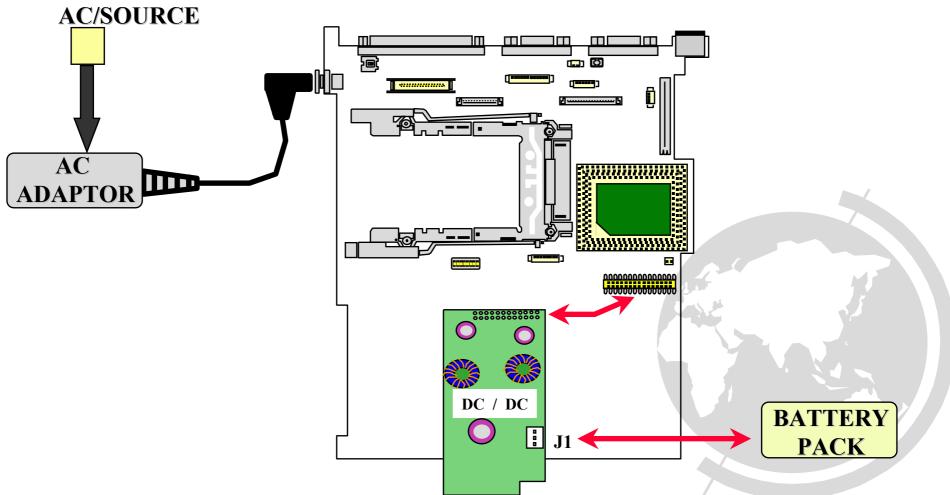

**2. LOCATION OF CONNECTORS & SWITCHES**

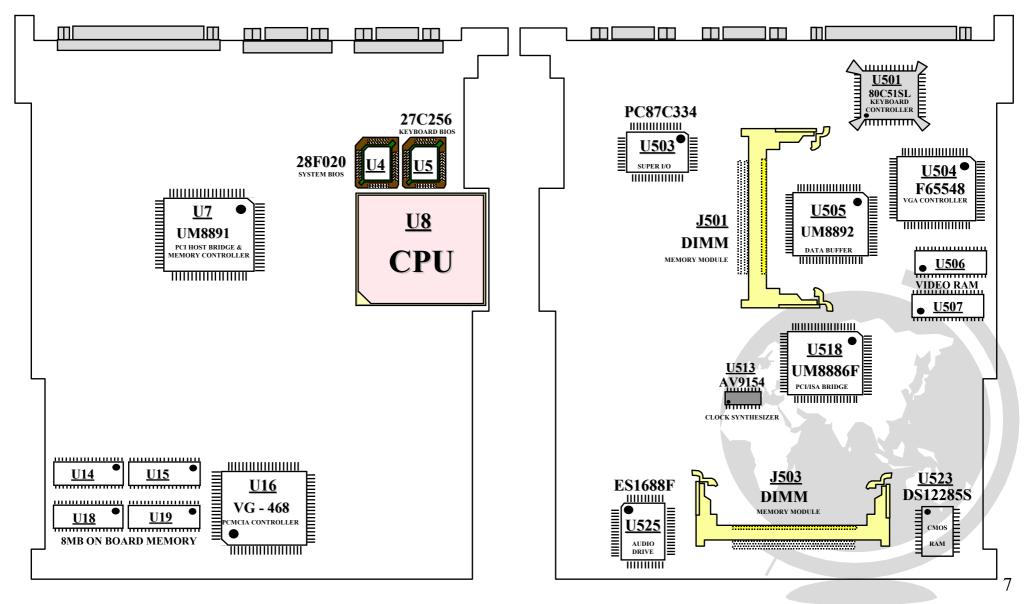

# **3. MAJOR COMPONENTS**

### **1. U8 PENTIUM PROCESSOR**

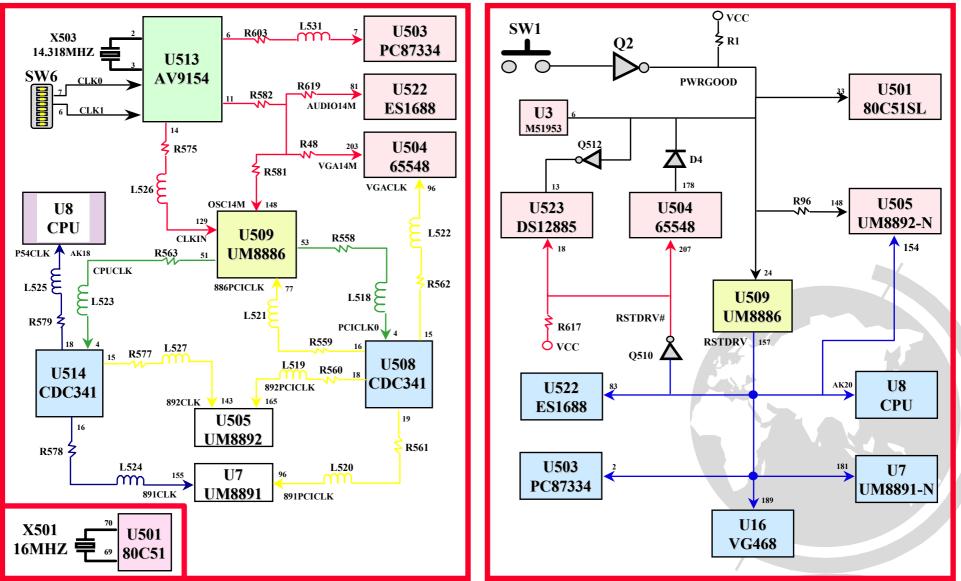

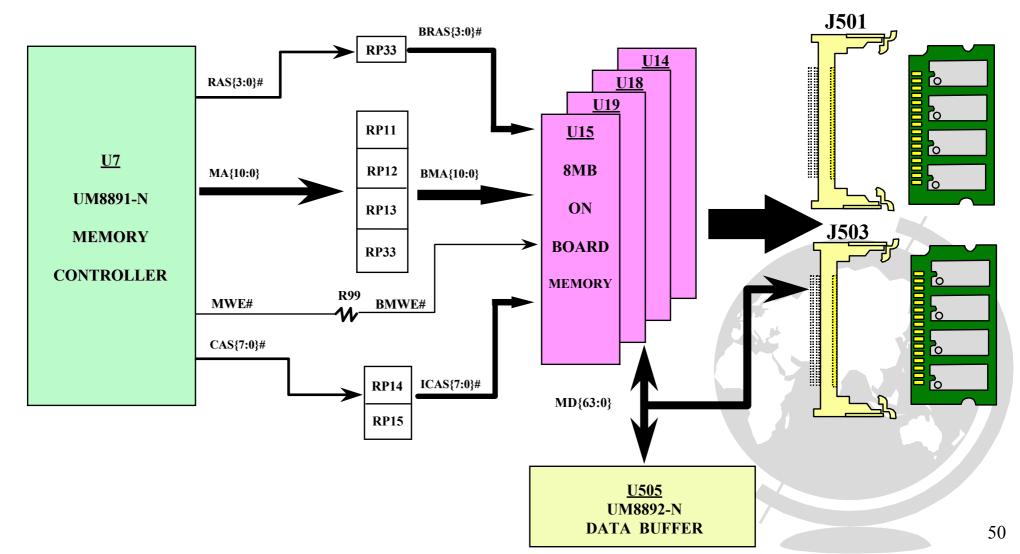

- 2. U7 UM8891BE/CYS PCI BRIDGE & MEMORY/CACHE CONTROLLER

- 3. U509 UM8886BE/CYS PCI TO ISA BRIDGE

- 4. U505 UM8892BE/CYS DATA PATH CONTROLLER

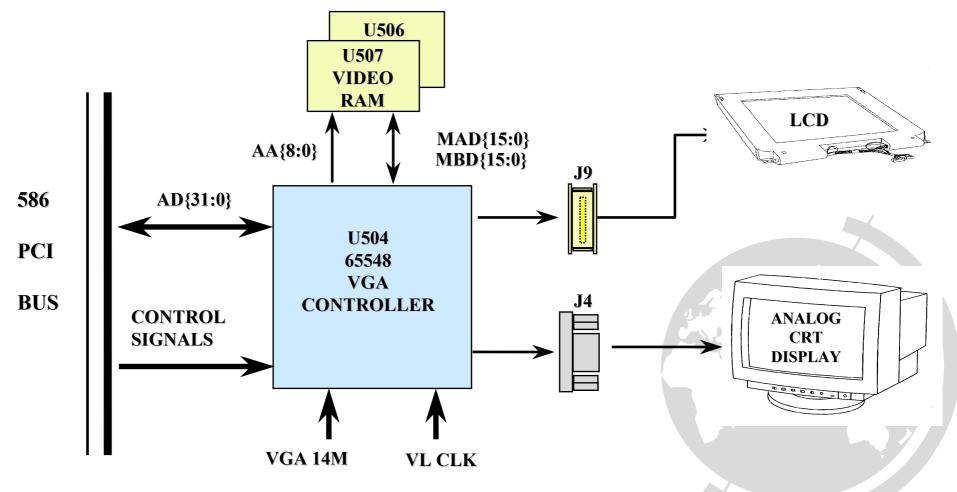

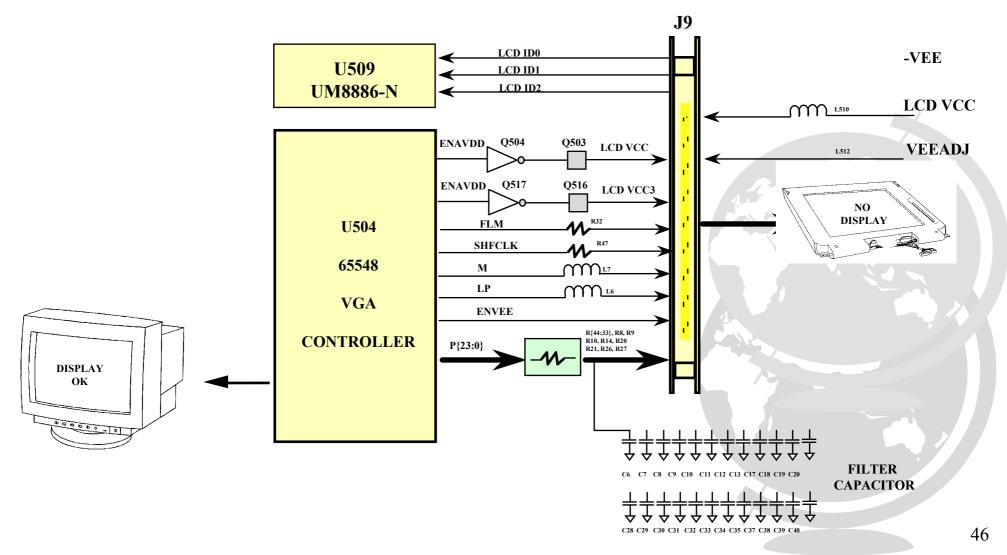

- 5. U504 C&T 65548 VGA CONTROLLER

- 6. U503 NS PC87334 SUPER I/O CONTROLLER

- 7. U16 VADEM VG-468 PCMCIA CONTROLLER

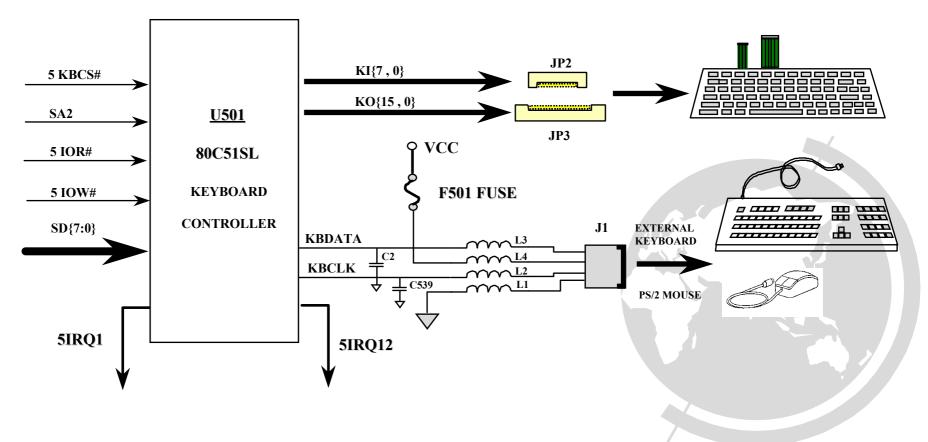

- 8. U501 80C51 KEYBOARD CONTROLLER

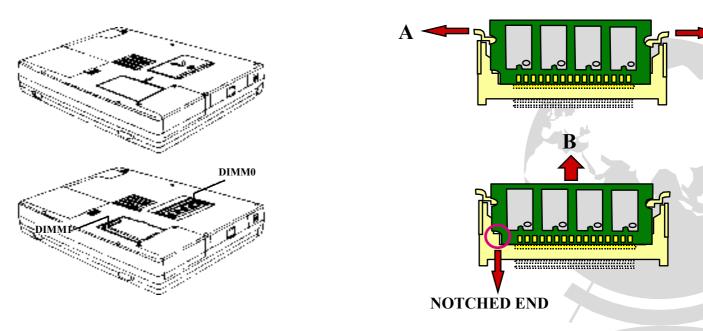

- 9. J501, J503 OPTIONAL DIMM SOCKETS

- **10. U510 VG-468 PCMCIA CONTROLLER**

- 11. U14, U15, U18, U19 8MB ON BOARD MEMORY

- **12. U4 SYSTEM BIOS**

- 13. U5 KEYBOARD BIOS

14. U514 AV9154 CLOCK GENERATOR

15. U522 ESS1688 AUDIO CONTROLLER

16. U523 DS12885 RTC CONTROLLER

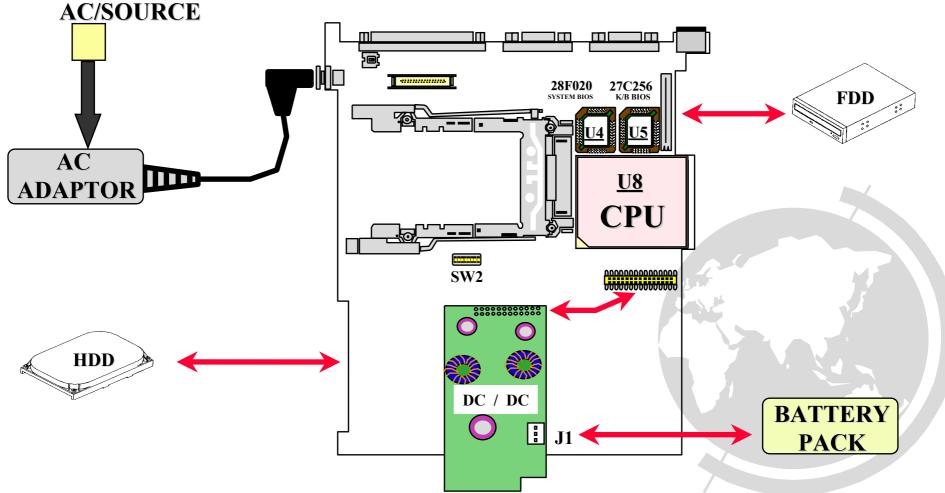

**4. LOCATION OF MAJOR COMPONENTS**

## **5. PIN DESCRIPTIONS OF MAJOR COMPONENTS**

#### **5.1 PENTIUM MICROPROCESSOR (P54LM)**

| SYMBOL    | TY PE | DESCRIPTION                                               |

|-----------|-------|-----------------------------------------------------------|

| A 20M #   | I     | w hen the address bit 20 mask pin is active, the 20 (A20) |

|           |       | PENTIJNM M CORPROCESSOR MASKS PHYSICAL ADDRES BI          |

|           |       | BEFORE PERFORM ING A LOOKUP TO THE INTERNAL CACHE OR      |

|           |       | EM ULATES THE ADDRESS W RAPAROUND AT THE AM B             |

|           |       | DRIVING A MEMORY BUS CYCLE ONTO THE BUSES.A20M #          |

|           |       | BOUNDARY THAT OCCUS ON THE 8086,8088.                     |

| A31:A5    | IO    | A 31 A 3 COM PRISE THR PENTIUM E ,CROPROCESSOR S ADDRES   |

| A4A3      | 0     | BUS.                                                      |

| ADS#      | IO    | W HEN ACTIVE ,THE ADDRESS STATUS OUTPUT INDICCATES        |

|           |       | THAT A VALID BUS CYCLE DEFINITION AND ADDRESS ARE         |

|           |       | AVALABLE ON THE BUS CYCLE DEFINITION AND BUS LINES.       |

| AHOLD     | I     | THE ADDRESS HOLD REQUEST INPUT ALLOW S ANOTHER BUS MAST-  |

|           |       | ER ACCESS TO PENTIUM MICROPROCESSOR S ADDRESS BUS FOR A   |

|           |       | CACHE INVALIDATION, BACK INVALIDATION, OR INQUIRE CYCLE.  |

| AP        | IO    | THE PENTIUM PROCESS GENERATES ADDRESS PARITY DURING       |

|           |       | M EM ORY W RIFE OPERATIONS AND CHECK ADDRESS PARIFY       |

|           |       | DURING CACHE INVALIDATION CYCLES (ADDRESS BUS SNOOPING ). |

| APCHK#    | 0     | THE PENTIUM PROCESS ASSERTS THE ADDRES PARITY CHECK       |

|           |       | OUTPUT W HEN AN ADDRES BUS PAR ITY ERROD IS DETECTED      |

|           |       | APCHK# IS ASSERTED 2 CLOCK CYCLES AFTER EADS# IS          |

|           |       | SAM PLE ACTIVE . APCHK\$ REM AIN ACTIVE FOR ON CLOCK      |

|           |       | CYCLE.                                                    |

| [APICHEN] | IO    | APT ENABLE.                                               |

| or picd1  |       |                                                           |

| BE0#      | 0     | BYTE ENABLE PATHO (D7D0).                                 |

| BE1#      | 0     | BYTE ENABLE PATH1 (D15D8).                                |

| BE2#      | 0     | BYTE ENABLE, PATH 2 (D23D16).                             |

| BE3#      | 0     | byte enable, path3 (D31:D24).                             |

| BE4#      | 0     | BYTE ENABLE, PATH4 (D 39 D 32).                           |

| BE5#      | 0     | BYTE ENABLE, PATH5 (D47:D40).                             |

| BE6#      | 0     | BYTE ENABLE, PATH6 (D55:D48).                             |

| BE7#      | 0     | BYTE ENABLE, PATH7 (D63D56).                              |

| SYMBOL    | TY PE | DESCRIPTION                                                                  |

|-----------|-------|------------------------------------------------------------------------------|

| BF        | I     | THE BUS FREQUENCY SIGNAL (BF) DETE RM INES THE IO BUS                        |

|           |       | TO PROCESSOR CORE FREQUENCY RATIO.                                           |

| BOFF#     | I     | ENSURE THAT THE PROCESSOR DOESN T FETCH STALE DATA                           |

|           |       | FROM MAIN MEMORY.                                                            |

| BP3:2     | 0     | THE BREAK POINT OUTPUTS INDICATE THAT A BREAKPOINT                           |

|           |       | MATCH HAS BEEN DETECTED THROUGH THE BRESKPOINT                               |

|           |       | REGISTER.                                                                    |

| BP/PM 1:0 | 0     | BREAKPOINT AND PERFORMANCE MONITORING PINS.                                  |

| BRDY#     | I     | THE BURS READY INPUT INDICATES THAT THE CURRENTLY ADDRE                      |

|           |       | SSED DEVICE HAS PRESENTED VALID DATA ON THE DATA BUS PINS                    |

|           |       | ${\rm I\!N}$ response to a read or that currently addressed dev ${\rm I\!C}$ |

|           |       | HAS ACCEPTED DATA FROM THE PENTIUM CPU IN RESPONSE TO A                      |

|           |       | WRITE.                                                                       |

| BRDCY#    | I     | THE BURS READY NPUT INDICATES THAT THE LEVEL 2 CACHE HAS                     |

|           |       | PRESENTED VALD DATA ON THE DATA BUS PINS IN RESPONSE TO A                    |

|           |       | READ OR THAT THE LEVEL 2 CACHE HAS ACCEPTED DATA FROM                        |

|           |       | THE PENTIUM CPU IN RESPONSE TO A WRITE.                                      |

| BREQ#     | 0     | THE INTERNAL CYCLE PENDING OUTPUT INDICATES THAT THE                         |

|           |       | PENTIM M CROCESSOR HAS A BUS CYCLE REQUEST PENDING.                          |

| BT3BT0    | NA    | BRANCH TRACE LINES ARE DRIVEN DURING A BRANCH TRACE                          |

|           |       | SPECIAL CYCLE.                                                               |

| BUSCHK#   | I     | THE BUS CHECK ALLOW S SYSTEM DESIGNERS TO NOTIFY THE CPU                     |

|           |       | F A BUS CYCLE HAS NOT COM PLETED SUCCESSFULLY.                               |

| CACHE#    | IQ    | CACHE# SIGNAL IS ACTIVE W HEN INFORMATION IS BEGIN                           |

|           |       | TRANSFREED BETW EEN EXTERNAL MEMORY AND AN INTERNAL                          |

|           |       | CACHE.                                                                       |

| CLK       | I     | CLOCK PROVIDES THE FUNDAMINTAL TIM ING AND THE INTERNAL                      |

|           |       | OPERATING FREQUENCY FOR THEE PENTIUM M ICROPROCESSOR                         |

| CPUTYP    | I     | CPU TYPE PN SAM PLED BY THE PROCESSOR AT THE TRALNG-                         |

|           |       | EDGE OF RESET TO DETERM INE W HETHER IT IS PRIMARY OR THE                    |

|           |       | DUAL PROCESSPR .                                                             |

## **5. PIN DESCRIPTIONS OF MAJOR COMPONENTS**

#### **5.1 PENTIUM MICROPROCESSOR (P54LM)**

| SYMBOL  | TY PE | DESCRIPTION                                                                           |

|---------|-------|---------------------------------------------------------------------------------------|

| D7:D0   | ΙO    | DATA PATH ZERO.                                                                       |

| D51:D8  | ĨŎ    | DATA PATH ONE.                                                                        |

| D23D16  | ĨQ    | DATA PATH TW O.                                                                       |

| D31:D24 | ΙÖ    | data path three.                                                                      |

| D39D32  | ΙÓ    | DATA PATH FOUR.                                                                       |

| D47:D40 | ΙÓ    | DATA PATH FIVE.                                                                       |

| D55:D48 | ΙÓ    | DATA PATH SK.                                                                         |

| D63D56  | IQ    | data path seven.                                                                      |

| D/C#    | ΙØ    | DATA OR CONTROL.AT THE START OF BUS CYCLE, THE PENTIUM                                |

|         |       | processor sets this line high if data w ill be transfered                             |

|         |       | DURING THE CURRENT BUS CYCLE OTHERW ISE SETS IN TO LOW .                              |

| D /P#   | 0     | DUAL/PRIMARY .THIS IS AN OUTPUT OF PRIMARY PROCESSOR AND                              |

|         |       | IS NOT USED BY THE DUAL PROCESSOR $\ensuremath{\mathrm{I\!T}}$ ASSERTED (LOW ) BY THE |

|         |       | PRIMARY PROCESSOR W HEN IT HAS ACQUIRED PRIVATE BUS OW N-                             |

|         |       | ership and has initiated a bus cycle                                                  |

| DPO     | ΙO    | PARITY BI FOR DATA PATH 0,0700.                                                       |

| DP1     | ΙÓ    | pariny bit for data path 1,015:08.                                                    |

| DP2     | ĨQ    | PARITY BI FOR DATA PATH 2D23D16.                                                      |

| DP3     | ΙÖ    | PARITY BIT FOR DATA PATH 3,D31 D24.                                                   |

| DP4     | ĨQ    | parity bit for data path 4,039,032.                                                   |

| DP5     | ΙÓ    | PARITY BIT FOR DATA PATH 5,047:040.                                                   |

| DP6     | ĨQ    | parity bit for data path 6,055,048.                                                   |

| DP7     | ΙQ    | PARITY BI FOR DATA PATH 7,063,056.                                                    |

| DPEN#   | ΙO    | DUAL PROCESSOR ENABLE.                                                                |

| EADS#   | I     | THE EXTERNAL ADDRESS STROBE SIGNAL INDICATES THAT A VALID                             |

|         |       | external address has been driven onto the pentium s a $4$ a $3$                       |

|         |       | ADDRESS LINES BY ANOTHER MASTER.                                                      |

| EW BE#  | I     | THE EXTERNAL W RITE BUFFER EM PTY IS USED TO ENSURE THAT                              |

|         |       | MEMORY OPERATIONS OCCUR IN ORDER OF EXECUTION.                                        |

| FLUSH#  | I     | THE CACHE FLUSH INPUT FORCES FORCES THE PENTIUM ROCE-                                 |

|         |       | SSOR TO FLUSH THE CONTENTS IN OF ITS INTERNAL CACHE.                                  |

| FERR#   | 0     | FLOATINGOPOINT ERROR OUTPUT PIN IS DRIVEN ACTIVE W HEN A                              |

|         |       | FLOATING-POINT ERROR OCCURS.                                                          |

| SYMBOL   | TY PE | DESCRIPTION                                              |

|----------|-------|----------------------------------------------------------|

| FRCMC#   | I     | THE FUNCTOIN REDUNDANCY CHECKING MASTER CHECKER# PIN IS  |

| 11101101 | -     | SAM PLED BY THE PENTIM M CROPROCESSOR DURING RESET TO    |

|          |       | DETERM INE W HETHER THE M ICROPROCESSOR SHOULD BE CONFIG |

|          |       | ED AS A FUNCTIONAL REDUNDANCY MASTER OR CHECKER.         |

| нт#      | IQ    | THE HIT # SUNAL ACTIVE TO INDICATE A SNOOP HIT IN EITHER |

|          | 10    | THE INTERNAL CODE OR DATA CACHE.                         |

| HITM #   | τØ    | THE PENTIUM M COPROCESSOR DRIVES THE HI MODIFIED         |

| пты #    | 10    | SIGNAL ACTIVE TO INDICATE A SNOOP HIT TO A MODIFIED      |

|          |       | LINE IN THE DATA CACHE.                                  |

|          | 70    |                                                          |

| HLDA     | IO    | BUS HOLD ACKNOW LEDGE.                                   |

| HOLD     | I     | THE BUS HOLD REQUEST INPUT ALLOW S ANOTHER BUS MASTER    |

|          |       | TO GAIN COM PLETE CONTROL OF THE PENTIUM S LOCAL BUSES.  |

| BT       | NA    | THE INSTRUCTION BRANCH TAKEN SIGNAL IS DRIVEN ACTIVE FOR |

|          |       | ONE CLOCK CYCLE W HEN PENTIUM M CROPROCESSOE EXECUTES    |

|          |       | AN INSTRUCTION RESULTING IN AN EXECUTION BRANCH.         |

| ERR#     | 0     | INTERNAL ERROR IS ASSERTED WHEN A PARIFY ERROR IS ENCOU- |

|          |       | NTERED INSIDE THE PENTIUM MICROPROCESSOR.                |

| GNNE#    | I     | GNORE NUM ERIC ERROR INPUT IS ASSERTED BY EXTERNAL LOGIC |

|          |       | THE PENTIUM MICROPROCESSOR WILL GNORE A NUMERIC ERROR    |

|          |       | AND CONTINUE EXECUTING NON-CONTROL FLOATING-POINT INSTRU |

|          |       | CTDNS.                                                   |

| NT       | I     | PENTIUM M CROCESSOR INIT INPUT HASTHE SAME EFFECT AS     |

|          |       | THE RESET SIGNAL EXCEPT THAT THE FOLLOW NG RETAIN        |

|          |       | THE VALUES.                                              |

| INTR     | I     | THIS IS MASKABLE INTERRUPT REQUEST INPUT.                |

| INV      | I     | THE INVALIDATE INPUT TELLS THE PENTIUM M CROPROCESSOR    |

|          |       | W HETHER THE CACHE LINE STATE SHOULD BE MARKED INVALIDAT |

|          |       | ED OR SHARED AS A RESULT OF SNOOP HIT.                   |

| IJ       | NA    | THE IJ SIGNAL ID CATED THAT AN INSTRUCTION IN THE "u"    |

|          |       | PIPLINE HAS COM PLETED EXECUTION.                        |

| V        | NA    | THE U SIGNAL DICATED THAT AN INSTRUCTION IN THE "V"      |

|          |       | PIPLNE HAS COM PLETED EXECUTION.                         |

## **5. PIN DESCRIPTIONS OF MAJOR COMPONENTS**

#### **5.1 PENTIUM MICROPROCESSOR (P54LM)**

| SYMBOL   | TY PE | DESCRIPTION                                                                                                                                                                                                               |

|----------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| KEN#     | I     | THE CACHE ENABLE PIN IS SAM PLED TO DETERM INE IF THE                                                                                                                                                                     |

|          |       | CURRENT BUS CYCLE IS CACHEABLE.                                                                                                                                                                                           |

| LINTO OR | I     | IF THE PROCESSOR S LOCAL APIC IS ENABLE, THIS IS THE                                                                                                                                                                      |

| 1NTR     |       | LINTO INPUT TO THE APIC .                                                                                                                                                                                                 |

| LOCK#    | ΪQ    | THE LOCK#SIGNAL IS ASSERTED WHEN THE PENTIUM                                                                                                                                                                              |

|          |       | M ICROPROCESSOR W ANTS TO RUN MULTIP BUS CYCLES                                                                                                                                                                           |

|          |       | w ITHOUT HAVING THE BUSES TAKEN AW AY BY ANOTHER BUS                                                                                                                                                                      |

|          |       | MASTER.                                                                                                                                                                                                                   |

| M/ID#    | ΪQ    | MEMORY OR IO.AT THE START OF BUS CYCLE, THE PENTIUM                                                                                                                                                                       |

|          |       | processor sets this line high if addressing a memory loc-                                                                                                                                                                 |

|          |       | ATION AND LOW IF ADDRESSING AN IO LOCATION.                                                                                                                                                                               |

| NA#      | I     | THE NEXT ADDRESS INPUT INDICATES THAT THE MEMORY                                                                                                                                                                          |

|          |       | SUBSYSTEM IS CAPABLE FO TAKING ADVANTAGE OF THE                                                                                                                                                                           |

|          |       | PENTIUM MICROPROCESSOR SADDRESS PIPELINING.                                                                                                                                                                               |

| NM I     | I     | NON-MASKABLE INTERRUPT REQUEST.                                                                                                                                                                                           |

| PBREQ#   | ΙØ    | $\operatorname{pr}\operatorname{I\!NATE}$ bus request only used $\operatorname{I\!N}$ dual processor system .                                                                                                             |

| PBGNT#   | ΙØ    | $\operatorname{pr}\operatorname{I\!N}\operatorname{ate}\operatorname{bus}\operatorname{grant}\operatorname{only}\operatorname{used}\operatorname{I\!N}\operatorname{dual}\operatorname{processor}\operatorname{system}$ . |

| PCHK#    | 0     | SEE DPO.                                                                                                                                                                                                                  |

| PCD      | 0     | PAGE CACHE DISABLE.                                                                                                                                                                                                       |

| PEN#     | I     | PARITY ENABLE.                                                                                                                                                                                                            |

| PH II #  | ΪQ    | PAR NATE BUS HIT PHIT IS AN OUTPUT FROM THE LRM AND AN                                                                                                                                                                    |

|          |       | $\operatorname{I\!N}\operatorname{PUT}$ to the MRM IIIS USED $\operatorname{I\!N}$ A dual processor sytem .                                                                                                               |

| PHIM #   | ī/O   | PRIVATE BUSHITON MODIFIED LINE.                                                                                                                                                                                           |

| PICCLK   | I     | PROGRAMMABLE INTERRUPT CONTROLLER CLOCK.                                                                                                                                                                                  |

| PICDO OR | ΙØ    | PROGRAMMABLE INTERRUPT CONTROLLER DATA LINEO.                                                                                                                                                                             |

| DEPN#    |       |                                                                                                                                                                                                                           |

| PICD1OR  | ΪQ    | PROGRAMMABLE INTERRUPT CONTROLLER DATA LINE1.                                                                                                                                                                             |

| APICEN   |       |                                                                                                                                                                                                                           |

| PRDY     | 0     | PROBE READY ASSERTED BY THE PROCESSOR W HEN IT HAS STOP-                                                                                                                                                                  |

|          |       | PED EXECUTION IN RESPONSE TO THE RASHSIGNAL BEING ASSERTED                                                                                                                                                                |

|          |       | LOW .                                                                                                                                                                                                                     |

| PW T     | 0     | THE PAGE W RIFE-THROUGHT PIN REFLECTS THE STATE OF THE                                                                                                                                                                    |

|          |       | PAGE ATTRIBUTE BIT.                                                                                                                                                                                                       |

| SYMBOL   | TY PE | DESCRIPTION                                                 |

|----------|-------|-------------------------------------------------------------|

| RESET    | I     | 1 KEEPS THE M ICROPROCESSOR FROM OPERATING UNTIL THE        |

|          |       | Pow er supply voltages have come up and stsbilded.          |

|          |       | 2 FORCES KNOW N DEFAULT VALUES INTO THE PENTIUM             |

|          |       | PROCESSOR REGISTER.                                         |

| R /S#    | I     | RUN/STOP.W HEN SET HIGH , THE PROCESSOR IS PERM IITED TO    |

|          |       | RUN NORMALLY W HEN SET LOW , THE PROCESSOR CEASES TO        |

|          |       | EXECUTE INSTRUCTIONS AND ENTERS PROBE MODE.                 |

| SCYC     | IO    | SPLIT CYCLE IS VALID FOR LOCKED BUS CYCLES OLY SCYC IS      |

|          |       | ASSERTED W HEN A LOCKED TRANSFER RESULTS IN A M ISALIGNED   |

|          |       | MWMORYACCESS.                                               |

| SM IH    | I     | SYSTEM MANAGEMENT INTERRUPT INFORMS THE PROCESSOR           |

|          |       | THAT A SYSTEM MANAGEMENT INTERRUPT ROUTINE RESIDING IN      |

|          |       | SYSTEM MANAGEMENT ADDRESS SPACE NEEDS TO BE PERFORME        |

| SM ICAT# | 0     | SYSTEM MANAGEMENT INTERRUPT ACKNOW EDGW INFORMS EXTE        |

|          |       | RNAL LOGIC THAT THE PROCESSOR IS IN SYSTEM MANAGEMENT       |

|          |       | MODE.                                                       |

| TCK      | I     | TEST CLOCK USED TO CLOCK STATE INFORMATION AND DATA INT     |

|          |       | AND OUT OF DEVICE DURING BOUNDARY SCAN.                     |

| TDI      | I     | TEST NPUT USED TO SHIFT DATA AND INSTRUCTIONS INTO THE      |

|          |       | TEST ACCESS PORT IN A SERIAL BIT STREAM .                   |

| TDO      | 0     | test output used to shift data out of the test access por   |

|          |       | IN A SERIAL BIT STREAM .                                    |

| TM S     | I     | TEST M ODE SELECT USED TO CONTROL THE STATE OF THE TEST     |

|          |       | ACCESS PORT CONTROLLER .                                    |

| TRST#    | I     | TEST RESET USED TO FORCE THE TEST ACCESS PORT CONTROLLED    |

|          |       | NTO AN NITALIZED STATE.                                     |

| ₩В/₩Т#   | I     | THE WRITE-BACK OR WRITE THROUGH INPUT ALLOW S EXTERNAL      |

|          |       | logic to determ ine w hether a is placed in the w rite back |

|          |       | OR W RITE THROUGH STATE.                                    |

| W/R#     | ĨŎ    | W RITE OR READ AT THE START OF A BUS CYCLE THE PENTION      |

|          |       | PROCESSOR SETS THIS LINE HIGH IF THE CURRENT BUS CYCLE IS   |

|          |       | WRITE BUS CYCLE W R # IS SET LOW IF THE CURRENT BUS CYCLE   |

|          |       | IS A READ BUS CYCLE.                                        |

10

# **5. PIN DESCRIPTIONS OF MAJOR COMPONENTS**

#### 5.2 UM8891-N PCI HOST BRIDGE AND MEMORY/CACHE CONTROLLER

| SYMBOL         | TY PE | DESCR PTION                                               |

|----------------|-------|-----------------------------------------------------------|

| CA4A           | 0     | CACHE RAM ADDRESS BIL. FOR ASYNCHRONOUS SECONDARY         |

|                | -     | CACHE RAM APPLICATION IT PROVIDES SYSTEM ADDRES BIT       |

|                |       | 4 FOR BANK A.                                             |

| CA4B           | 0     | CACHE RAM ADDRESS BIT.FOR ASYNCHRONOUS SECONDARY          |

| 011 10         | Ű     | CACHE RAM APPLICATION IT PROVIDES SYSTEM ADDRES BIT       |

|                |       | 4 FOR BANK B.                                             |

| CA3            | 0     | CACHE RAM ADDRESS BIL.FOR ASYNCHRONOUS SECONDARY          |

| CAS            | 0     | CACHE RAM ADDRESS BILFOR ASTNCHRONOUS SECONDART           |

|                |       | 3. FOR SYNCHRONOUS SECONDARY CACHE RAM APPLICATION.       |

| 000014004      | 0     |                                                           |

| CRCSA#/CE#     | 0     | CACHE RAM CHIP SELECT FOR BANK A.                         |

| CRCSB#/ADSC#   | 0     | CACHE RAM CHIP SELECT FOR BANK B.                         |

| CROEA#/OE#     | 0     | CACHE RAM OUTPUT ENABLE FOR BANK A.                       |

| CROEB#/ADV#    | 0     | CACHE RAM OUTPUT ENABLE FOR BANK A.                       |

| CRW [7:0]      | 0     | CACHE RAM WRITE CONTROL.SECONDARY CACHERAM WR-            |

|                |       | ITE CONTROL SIGNALS W ITH RESPECT TO EACH BYTE.           |

| TA[7:0]        | ΙO    | ADDRESS TAG RAM DATA.                                     |

| TRW R#         | 0     | ADDRESS TAG RAM WRITE CONTROL SIGNAL.                     |

| PALTH          | 0     | PROCESS ADDRESS LATCH CONTROL SIGNAL.                     |

| M DPERR#       | I     | MEMORY DATA PARITY ERROR . INPUT FROM UM 8892N .IND I-    |

|                |       | CATES THERE IS A PARITY ERROR ON MD BUS.                  |

| ADPAR          | т     | PCIDATA PARITY .NPUT FROM UM 8892N . FOR 32-BIT DATA BUS  |

|                | -     | PARITY.                                                   |

| PDCTL[3:0]     | 0     | PCI DATA BUS CONTROLOUTPUT TO UM 8892N.CONTROL PD         |

| PDC111[3:0]    | 0     | BUS DIRECTION AND LATCH FUNCTIONS.                        |

| M D G MT [240] | 0     |                                                           |

| M DCTL[3:0]    | 0     | M EM ORY DATA BUS CONTROL.OUTPUT TO UM 8892N.CONTROL      |

|                |       | THE M D BUS DIRECTION AND LATCH FUNCTION.                 |

| ADCTL[3:0]     | 0     | PCIDATA BUS CONTROL.OUTPUT TO UM 8892N.CONTROL AD         |

|                |       | BUS DIRECTION AND LATCH FUNCTION.                         |

| AD[31:0]       | ΙO    | 32-BIT PCIADDRESS AND DATA BUS.                           |

| FRAM E#        | IQ    | PCIBUS TRDY#SIGNAL.CYCLE FRAME.OUTPUT WHEN UM 891N        |

|                |       | ACTS AS CURRENT PCIBUS IN IT ATOR; OTHERW ISE, IT IS AN   |

|                |       | INPUT PIN FRAME# IS DEASSERTED TO INDICATE THAT THE       |

|                |       | IN IT TATOR IS READY TO COM PLETE THE FINAL DATA PHASE.   |

| PCICLK         | I     | PCIBUS CLOCK                                              |

| CBE#[3:0]      | ΙO    | PCIBUS COMMAND AND BYTE ENABLE SIGNALS                    |

| PAR            | IQ    | PCIBUS PARITY BIT                                         |

| SERR#          | 0     | PCIBUS SERR# SIGNAL                                       |

| LOCK#          | ΙO    | PCIBUS LOCK# SIGNAL .NDICATES A LOCK CYCLE.               |

| STOP#          | TO    | PCIBUS STOP# SIGNAL OUTPUT W HEN UM 8891 ACTS AS A TAR-   |

| 0101 11        | 10    | GET OF PCIBUS CYCLE TO INDICATE THAT IT REQUESTS THE      |

|                |       | NITATOR TO STOP THE TRANSACTION IN PROGRESS ON THE        |

|                |       |                                                           |

| D DI CODT II   |       | CURRENT DATA PHASE: OTHER IT IS AN OUTPUT PIN.            |

| DEVSEL#        | IQ    | PCIBUS DEVSEL# SIGNAL. DEVICE SELECT ASSERTED W HEN       |

|                |       | UM 8891N DECODING LOGIC IS TRUE OTHERW ISE IT IS AN INPUT |

|                |       | PN.                                                       |

| TRDY#          | IQ    | PCIBUS TRDY# SIGNAL. TARGET READY .IT IS ASSERTED W HEN   |

|                |       | UM 8891N IS READY TO COM PLETE THE CURRENT DATA PHASE.    |

| IRDY#          | IQ    | PCIBUS IRDY# SIGNAL. IN IT IATOR READY. DUR ING A W RITE, |

|                |       | IRDY#ASSERTED INDICATES THAT THE INITIATOR IS DRIVING     |

|                | 1     | VALID DATA ONTO THE DATA BUS DURING A READ , IRDY # ASS-  |

|                |       | ERTED INDICATES THAT THE INITIATOR IS READY TO ACCEPT     |

|                | 1     | DATA FROM THE TARGET.                                     |

| REQ#           | 0     | PCIBUS REQUEST .                                          |

| GNT#           | T     | PCIBUS GRANT.                                             |

| MWE#           | 0     | DRAM W RITE ENABLE                                        |

| MA[11:0]       | 0     | DRAM WRITE ENABLE<br>DRAM ADDRESS SIGNALS                 |

|                |       |                                                           |

| CAS[7:0]       | 0     | DRAM COLUMN SIGNAL STROBE                                 |

| SYMBOL      | TYPE | DESCRIPTION                                                                                                       |

|-------------|------|-------------------------------------------------------------------------------------------------------------------|

| RAS[5:0]    | 0    | DRAM ROW SIGNAL STROBE                                                                                            |

| RAS[7:6]    | 0    | DRAM ROW SIGNAL STROBE                                                                                            |

| PA [31:0]   | ΙO   | PROCESSOR ADDRESS BUS.                                                                                            |

| PBE7#-PBE0# | I    | BYTE ENABLE.                                                                                                      |

| ADS#        | I    | ADDRESS STROBE. INDICATES THAT A NEW VALID BUS CYCLE<br>IS CURRENTLY BEING DRIVEN BY THE CPU.                     |

| PM ID       | т    | MEMORY OR TO ACCESS DEFINES WHETHER THE CURRENT                                                                   |

|             | -    | CPU CYCLE IS A MEMORY OR IO ACCESS.                                                                               |

| PW R        | I    | W RIFE OR READ ACCESS DEFINES W HETHER THE CURRENT<br>CPU CYCLE IS A W RIFE OR READ ACCESS.                       |

| PDC         | I    | DATA OR CODE ACCESS DEFINES W HETHER THE CURRENT                                                                  |

| DI O GIV #  | т    | CPU CYCLE IS A DATA OR CODE ACCESS.                                                                               |

| PLOCK#      | 1    | BUS LOCK . IND ICATES THAT CURRENT CPU BUS CYCLES SHO-                                                            |

|             |      | ULD NOT BE INTERRUPTED SUCH AS WHEN THE CPU IS RUNNI-                                                             |

|             |      | NG A READ-MODIFY-WRITE CYCLE OR INTERRUPT ACKNOW LE-                                                              |

|             | _    | DGE CYCLE.                                                                                                        |

| CACHE#      | I    | CACHE-ABLIIY. NDICATES CPU INTERNAL CACHE-ABLIIY<br>FOR THE CURRENT CYCLE.                                        |

| HITM #      | I    | HIM ISS TO A MODIFIED LINE INDICATES THE CURRENT INO-                                                             |

| пшп #       | -    | URE CYCLE HIT A MODIFIED LINE IN CPU DATA CACHE AND                                                               |

|             |      |                                                                                                                   |

| DUOID       | 0    | CPU W ILL SCHEDULE A W RITE-BACK CYCLE TO THE BUS.                                                                |

| PHOLD       | 0    | CPU HOLD.                                                                                                         |

| PHLDA       | I    | CPU BUS HOLD ACKNOW LEDGE.                                                                                        |

| BOFF#       | 0    | BACK-OFF THIS SIGNAL IS USED TO FORCE CPU OFF THE BUS<br>IN THE NEXT CLOCK .                                      |

| KEN#        | 0    | CACHE ENABLE .                                                                                                    |

| BRDY#       | 0    | BURST-OFF.THIS SIGNAL INDICATES TO THE CPU THAT THE                                                               |

| DICD I #    | Ŭ    | VALD DATA IS ON THE DATA BUS IN RESPONSE TO A READ                                                                |

|             |      | CYCLE OR THE DATA PROVIDED BY CPU HAS BEEN ACCEPTED                                                               |

|             |      | IN RESPONSE TO A W RITE CYCLE.                                                                                    |

| W BW T#     | 0    | RESERVED                                                                                                          |

|             |      |                                                                                                                   |

| NA#         | 0    | NEXT ADDRESS. THIS SIGNAL NDICATES TO THE CPU THAT                                                                |

|             | -    | UM 8891 IS READY TO ACCEPT A NEW BUS CYCLE.                                                                       |

| INV OT4     | 0    | INVALIDATION REQUEST. THIS SIGNAL INDICATES TO THE CPU<br>TO DETERM INE THE FINAL STATE OF A CACHE LINE AS A RES- |

|             |      | ULT OF AN NQURE HIT.                                                                                              |

| EADS#       | 0    | EXTERNAL ADDRESS STROBE.                                                                                          |

| SM IACT#    | I    | SYSTEM MANAGEMENT INTERRUPT ACTIVE INDICATES THAT                                                                 |

|             |      | THE CPU IS OPERATING IN SMM.                                                                                      |

| SUSPA       | I    | SUSPENT ACKNOW LEDGE FOR CYRIX CPU                                                                                |

| REFRESH#    | I    | REFREAH REQUEST INPUT                                                                                             |

| RESET       | I    | RESET .THIS IS A SIGNAL OF 8891N                                                                                  |

| CLK         | I    | CPU CLOCK INPUT                                                                                                   |

| CLKDC       | I    | INPUT FROM UM 8886N TO NOTIFY UM 8891N                                                                            |

| CLKRUN#     | 0    | RESERVED                                                                                                          |

| SCLKCTL     | 0    | SSYNCHRONOUS SRAM CLOCK CONTROL.                                                                                  |

| CPUPD       | I    | NOTIFY UM 8891N THAT CPU IS POW ER-DOW N OR CLOCK D.C                                                             |

| 891BUSY#    | 0    | RESERVED                                                                                                          |

| TESTI       | Т    | TEST INPUT M UST BE LOW                                                                                           |

| TESTO       | 0    | TEST OUTPUTVCC5                                                                                                   |

| VCC5        | Ť    | 5V POW ER FOR PCIINTERFACE LOGIC                                                                                  |

| VCC3        | 1    | 3.3V POW ER FOR CCPU INTERFACE LOGI                                                                               |

| VCCD        |      | POW ER FOR DRAM INTERFACE                                                                                         |

| VCCS        | -    | POW ER FOR DRAM NIERFACE<br>POW ER FOR CACHE SRAM INTERFACE PINS                                                  |

|             | 1    |                                                                                                                   |

11

## **5. PIN DESCRIPTIONS OF MAJOR COMPONENTS**

#### 5.3 UM8892-N DATA PATH CONTROLLER

| SYMBOL                   | TY PE | DESCRIPTION                                                                                                                  |

|--------------------------|-------|------------------------------------------------------------------------------------------------------------------------------|

| PD[63:0] IO CPU DATA BUS |       | CPU DATA BUS                                                                                                                 |

|                          |       | data bus direction and internal latch are controlled by pdctl 3-0.                                                           |

|                          |       | FOUR BUFFERS STORE PD TO M D DATA.AND FOUR BUFFERS STORE PD TO AD DATA.                                                      |

| MD[63:0]                 | ΙØ    | M EM ORY DATA BUS                                                                                                            |

|                          |       | DATA BUS DIRECTION AND INTERNAL LATCH ARE CONTROLLED BY M DCTL2-0                                                            |

|                          |       | ONE BUFFER STORES MD TO AD DATA.                                                                                             |

| AD[31:0]                 | ΙØ    | PCIAD BUS                                                                                                                    |

|                          |       | DATA BUS DIRECTION AND INTERNAL LATCH ARE CONTROLLED BY ADCTL3-0.                                                            |

|                          |       | TW O 32BIT BUFFERS STORE AD TO PD DATA AND TW O 32BIT BUFFERS STORE AD TO MD DATA                                            |

| MDCTL[3:0]               | I     | M EM ORY DATA BUS CONTROL. NPUT FROM UM 8891N CONTROL M D M EM ORY DATA BUS<br>DIRECTION AND LATCH FUNCTION.                 |

| PDCTL[3:0]               | I     | CPU DATA BUS CONTROL.                                                                                                        |

|                          |       | INPUT FROM UM 8891N CONTROL PD (CPU DATA_BUS DIRECTION AND LATCH FUNCTION.                                                   |

| ADCTL[3:0]               | I     | PCIDATA BUS CONTROL.                                                                                                         |

|                          |       | INPUT FROM UM 8891N CONTROL AD (CPU DATA_BUS DIRECTION AND LATCH FUNCTION.                                                   |

| M DPERR#                 | 0     | M EM ORY DATE PARITY ERROR .OUTPUT TO UM 8891N, INDICATING A PARITY ERROR OCCURRED<br>ON M D BUS.(64-B IT M D PARITY CHECK ) |

| CTK                      | I     | CPU CLOCK                                                                                                                    |

| PCICLK                   | I     | PCIBUS CLOCK                                                                                                                 |

| ADPAR                    | 0     | PCIDATA PARITY.OUTPUT TO UM 8891N, FOR 32-BIT PCIDATA PARITY (EVEN PARITY)                                                   |

| DP[7:0]                  | ΙO    | PAR ITY FO M D BUS.                                                                                                          |

| VCCD                     |       | POW ER FOR DRAM INTERFACE.FOR 5V OR 3.3V DRAM APPLICATIONS.CONNECT THESE POW ER<br>PINTS TO 5V OR 3.3V                       |

| VCC5                     |       | POW ER PINS FOR 5V                                                                                                           |

| VCC3                     |       | POW ER FOR 3.3V                                                                                                              |

| GND                      |       | GROUNG                                                                                                                       |

## **5. PIN DESCRIPTIONS OF MAJOR COMPONENTS**

#### 5.4 UMC UM8886-N PCI TO ISA BRIDGE

| SYMBOL                     | TY PE | DESCRPTION                                                                           |

|----------------------------|-------|--------------------------------------------------------------------------------------|

| AD {31:0}                  | I/O   | 32 BIT PC IADDRESS AND DATA BUS                                                      |

| C/BE{3:0}                  | I/O   | PCIBUS COMMAND AND BYTE ENABLE SIGNALS                                               |

| DEVSEL#                    | ľQ    | PCIBUS DEVESEL SIGNAL. THIS ACTS AS AN OUTPUT PIN W HEN THE IBC                      |

|                            |       | IS THE SLAVE OF PCIBUS CYCLE TRANSACTION : OTHERW ISE. IT IS AN                      |

|                            |       | NPUT PN.                                                                             |

| TRDY#                      | I/O   | PCIBUS TRDY SIGNAL. THIS ACTS AN OUTPUT PIN W HEN THE IBC IS THE                     |

|                            |       | SLAVE OF PCIBUS CYCLE TRANSACTION : OTHERW ISE. IT IS AN INPUT                       |

|                            |       | PN.                                                                                  |

| IRDY#                      | I/O   | PCIBUS IRDY SIGNAL. THIS ACTS AS AN OUTPUT PIN W HEN THE IBC ISS-                    |

|                            |       | UES A CYCLE TO PCIBUS OTHERW ISE. IT IS AN INPUT PIN.                                |

| FRAM E#                    | I/O   | PCIBUS FRAME SIGNAL. THIS ACTS AS AN OUTPUT PIN W HEN THE IBC                        |

|                            |       | ISSUES A CYCLE TO PCIBUS OTHERW ISE. IT IS AN INPUT PIN.                             |

| IDSEL                      | I     | PCIBUS IDSEL INPUT SIGNAL. IDSEL IS USED AS CHIP SELECT DURING                       |

|                            |       | CONFIGURATION READ AND W RIFE TRANSACTION.                                           |

| PAR                        | 0     | PCIBUS PAR MY BM.                                                                    |

| SERR#                      | I     | SYSTEM ERROR.UPON SAMPLING THIS PIN ACTIVE.THE IBC GENERATES                         |

|                            |       | AN NM ITO THE CPU.                                                                   |

| LOCK#                      | I     | PCIBUS LOCK SIGNAL TO INDICATE LOCK CYCLE.                                           |

| STOP#                      | I/O   | PCIBUS STOP SIGNAL. THIS ACTS AS AN OUTPUT PIN W HEN THE IBC IS                      |

|                            |       | THE SLAVE OF PCIBUS CYCLE TRANSACTION : OTHERW ISE. IF IS AN                         |

|                            |       | NPUT PIN.                                                                            |

| <b>I</b> NT{D <b>:</b> A } | I     | PCIBUS INTERRUPT REQUEST A.B.C.D.                                                    |

| BCLK                       | 0     | ISA BUS CLOCK OUTPUT.                                                                |

| BALE                       | 0     | BUS ADDRESS LATCH ENABLE.                                                            |

| SA {19:0}                  | 0     | SYSTEM ADDRESS BUS SA $\{19:0\}$ .SA $\{19:0\}$ ARE OUTPUT.EXCEPT DUR $\mathbb{N}$ G |

|                            |       | ISA MASTER CYCLES.                                                                   |

| LA {23:}                   | 0     | latch-able address bus la {23:17} . la {23:17} are output . except                   |

|                            |       | DUR NG ISA MASTER CYCLES.                                                            |

| SBHE#                      | 0     | SYSTEM BUSHIGH ENABLE INDICATES THE HIGH BYTE ON THE ISA DATA                        |

|                            |       | BUS SD {15:8} IS VALID.                                                              |

| SD {15:0}                  | I/O   | 16 BIT ISA SYSTEM DATA BUS.                                                          |

| IDR#                       | 0     | ISA IO READ COMMAND.                                                                 |

| IOW #                      | 0     | ISA IO W RITE COMMAND.                                                               |

| M EM R #                   | 0     | ISA M EM ORY READ COM M AND .                                                        |

| MEMW#                      | 0     | ISA M EM ORY W R ITE COM M AND .                                                     |

| SYM BOL    | TY PE | DESCRPTION                                                            |

|------------|-------|-----------------------------------------------------------------------|

| SM EM R#   | 0     | ISA SYSTEM MEMORY READ COMMAND.                                       |

| SM EM W #  | 0     | ISA SYSTEM MEMORY WRITE COMMAND.                                      |

| DCS16#     | I     | 16-BIT 10. THIS SIGNAL INDICATES THAT BUS SIZE OF CURRENT ISA 10      |

|            |       | SLAVE IS 16 BITS.                                                     |

| M EM CS16# | ΙΌ    | 16-BIT MEMORY.THIS PIN INDICATES THAT THE BUS SIZE OF CURRENT         |

|            |       | ISA M EM ORY SLAVE IS 16 B IT.                                        |

| 0W S#/AC∎N | I     | NO W AIT STATES.THIS SIGNAL IS ASSERTED BY ISA SLAVE IN ORDER TO      |

|            |       | SHORTEN THE CYCLE.                                                    |

| DCHRDY     | ΙO    | CHANNEL READY. DCHRDY IS USED BY ISA SLAVES TO INSERT WAIT            |

|            |       | STATES.                                                               |

| M ASTER#   | I     | 16-B IT M ASTER . INDICATES THAT A 16-B IT ISA M ASTER HAS CONTROL OF |

|            |       | THE ISA BUS.                                                          |

| AEN        | 0     | ISA BUS AEN SIGNAL.WHEN HIGH. INDICATES THAT DMA OR REFRESH           |

|            |       | CONTROLS THE ISA BUS.                                                 |

| DCHCK#/    | I     | IO CHANNEL CHECK JBC W ILL GENERATE NM ITO CPU UPON SAM PLING         |

| CLKRUN#    |       | THIS PIN ACTIVE; CLKRUN IS RESERVED FOR FUTURE USE.                   |

| REFRESH#   | ΙÓ    | IO SYSTEM REFRESH CONTROL.OUTPUT TO ISA BUS W HEN CONVERTING          |

|            |       | SYSTEM TIMER TICKS INTO REFRESH CYCLE.                                |

| CPUREQ     | I     | CPU REQUEST.CPU NINATOR REQUESTS THE PCIBUS.                          |

| req 0# /   |       | al sur                                                                |

| COVERSW #  | I     | PCIM ASTER REQUEST 0.FOR REEQUESTS NITATED FROM PCIBUS                |

|            |       | MASTER.                                                               |

|            |       | COVERSW FROM EXTERNAL LCD COVER SW IICH TO INFORM THE PM U            |

|            |       | THAT THE LCD COVER HAD BEEN CLOSED SO THAT PM U CAN FORCE             |

|            |       | SYSTEM TO ENTER SUSPEND M ODE.                                        |

| REQ1#      | I     | PCIM ASTER REQUEST 1.                                                 |

| REQ2#/     | I     | PCIM ASTER REQUEST 2.                                                 |

| 891BUSY#   |       | THE 891BUSY IS RESERVED FOR FUTURE USE.                               |

| REQ3#/     | I     | PCIMASTER REQUEST 3. THIS PINALSO ACTS AS "COVERSW" FROM EXT-         |

| COVERSW #  |       | ERNAL LCD COVER SW IICH TO INFORM THE PM U THAT LCD COVER HAD         |

|            |       | BEEN CLOSED SO THAT PM U CAN FORCE SYSTEM ENTER SUSPEND MODE.         |

| GNT0# /    | 0     | PCIM ASTER GRANT 0. ARBITER HAS GRANTED PCIBUS MASTER OR AS           |

| NCLKDC#    |       | NCLKDC#UM 8886N W ILL FORCE NCLKDC#LOW TO INFORM UM 8891 THAT         |

|            |       | CPU CLOCK W ILL BE D.C.                                               |

| GNT1#      | 0     | PCIMASTER GRANT 0.                                                    |

## **5. PIN DESCRIPTIONS OF MAJOR COMPONENTS**

#### 5.4 UMC UM8886-N PCI TO ISA BRIDGE

| SYMBOL             | TY PE | DESCRPTION                                                        |

|--------------------|-------|-------------------------------------------------------------------|

| GNT2# /            | 0     | PCIMASTER GRANT 2.                                                |

| SUSP#              |       | THIS PIN ALSO ACTS AS SUSP#OUTPUT WHICH WILL BE FORCED LOW        |

|                    |       | AFTER ENTER NG SUSPEND MODE AND THE CLOCK TO CPU HAD BEEN         |

|                    |       | STOPED.                                                           |

| GNT3# /            | 0     | PCIMASTER GRANT 3.OR NCLKDC#UM 8886N W ILL FORCE NCLKDC#TO        |

| NCLKDC#            |       | LOW TO INFORM UM 8891 THAT CPU CLOCK W ILL BE D.C.                |

| X 32K              | I     | 32K CLOCK INPUT.                                                  |

| DREQ {3:0}         | I     | DM A REQUEST. THESE SIGNALS ARE USED TO REQUEST DM A SERVICE.     |

| DREQ {7:5}         |       |                                                                   |

| DACK#{7:0}         | IO    | DM A ACKNOW LEDGE.THE IBC ASSERTS THESE OUTPUT LINES TO INDICA    |

|                    |       | TE THAT THE DM A DEVICE HAS BEEN GRANTED SERVICE.                 |

| EOP                | IQ    | END OF PROCESS. IN INPUT MODE. THIS PIN IS USED BY THE DMA DEVICE |

|                    |       | TO STOP CURRENT DM A TRANSFER .IN OUTPUT MODE . DM A CONTROLLER   |

|                    |       | ASSERTS EOP TO INDICATE TO THE ACTIVE DM A DEVICE THAT THE TRAN   |

|                    |       | SFER HAS REACHED THE TERM INAL COUNT.                             |

| IRQ1               | I     | ISA BUS INTERRUPT REQUEST 1.                                      |

| IRQ {7:3}          | I     | ISA BUS INTERRUPT REQUEST {7:3}                                   |

| IRQ8               | I     | RTC INTERRUPT REQUEST.                                            |

| IRQ {12:9}         | I     | ISA BUS INTERRUPT REQUEST {12:9}                                  |

| <b>I</b> RQ{15:14} | I     | ISA BUS INTERRUPT REQUEST {15:14}                                 |

| NTR                | 0     | MASKABLE INTERRUPT TO CPU.                                        |

| NM I               | 0     | NONM ASKABLE INTERRUPT TO CPU.                                    |

| SM IH              | IQ    | SYSTEM MANAGEMENT INTERRUPT.OUTPUT TO CPU TO REQUEST SMM          |

|                    |       | SERVICE INPUT FROM CPU INDICATES THAT CPU HAS ENTERED SM M        |

|                    |       | MODE.                                                             |

| STPCLK#            | 0     | CPU SLOW DOWN /STOP CLOCK CONTROL.                                |

| PW RLCH2           | 0     | latch signal to latch pm C output pins from $sd{7:0}$ to generate |

|                    |       | PM CO-5.PM C8 AND CKGENPD.                                        |

| PW RLCH1           | 0     | latch signal to latch pm c output pins from $sd{7:0}$ to generate |

|                    |       | PM C6.PM C7/SUSP PM C8 PM C9 AND CLKSEL {2:0}.                    |

| EXTSM IH           | I     | EXTERNAL SM I1.                                                   |

| SM IACT#           | I     | SYSTEM MANAGEMENT INTERRUPT ACKNOW LEDGE FROM INTEL SL            |

|                    |       | ENHANCED CPU.                                                     |

| PCICLKI            | I     | PCIBUS CLOCK INPUT TO THE IBC.                                    |

| C LK IN            | I     | OSCILLATOR CLOCK INPUT TO GENERATE CPU AND PCICLOCKS.             |

| OSC                | I     | TIM E BASE 14.318 M HZ CLOCK INPUT.                               |

| HCLK               | 0     | CLOCK OUTPUT TO CPU HOST.                                         |

| PCICLK 0           | 0     | CLOCK OUTPUT TO PCIBUS.                                           |

| SYMBOL      | TY PE | DESCRPTION                                                                  |

|-------------|-------|-----------------------------------------------------------------------------|

| RSTIN       | I     | RESET NPUT:RSTN IS USED TO NITALIZE THE ENTIRE SYSTEM .                     |

| CPURST      | 0     | CPU RESET.THIS PIN IS USED TO INITIALIZE CPU.                               |

| RSTDRV      | 0     | ${\tt RSTDRV}$ . THIS PIN IS USED TO RESET ENTIRE SYSTEM , EXCEPT THE CPU . |

| KBCLK       | I/O   | KEYBOARD CONTROLLER CLOCK.CLOCK OUTPUT TO THE 8742.                         |

| RC/PGP0     | I/O   | RESETS INPUT FROM 8042, OR ACTS AS PROGRAM MABLE INPUT, OR OUT-             |

|             |       | PUT PIN 0.                                                                  |

| GA20/PGP1/  | I/O   | ADDRESS A20 GATE FROM 8042.OR ACTS AS PROGRAM MABLE INPUT/OU-               |

| LDEV#       |       | TPUT PIN 1.OR ACTS AS LOCAL DEVICE INPUT FROM VL BUS.                       |

| ROM CS#/    | 0     | ROM CS AND KBCS. DUAL FUNCTION PIN. FOR IO CYCLES, THIS PIN IS              |

| KBCS#       |       | KBCS:FOR MEMORY CYCLES, I IS ROMCS.                                         |

| SPKR        | 0     | SPEAKER DRIVE OUTPUT.                                                       |

| XDEN /PGP3  | 0     | XD BUS DIRECTION CONTROL. OR ACTS AS PROGRAM MABLE OUTPUT PIN               |

| TCRAM W R   |       | 3.0R AS TCRAM W R TO READ / R ITE EXTERNAL 4KB RTC.                         |

| RTCAS       | 0     | RTC ADDRESS LATCH.                                                          |

| RTCW R      | 0     | RTC W RITE COMMAND.                                                         |

| RTCRD       | 0     | RTC READ COMMAND.                                                           |

| DE1FX       | 0     | DE 1FX CHP SELECT.                                                          |

| IDE 3FX     | 0     | DE 3FX CH P SELECT.                                                         |

| ONOFF#/     | I     | "ON OFF" SW IICH INPUT TO PMU.SW IICHES BETW EEN FULL-ON MODE               |

| ACIN        |       | AND SUSPEND MODE OR ACTS AS AC IN.                                          |

| LB1/LB2     | I     | LOW BATTERY 1 OR LOW BATTERY 2 NPUT.                                        |

| IDE17X/     | 0     | DE 17X CHIP SELECT. OR ACTS AS PROGRAM MABLE OUTPUT PIN 3.                  |

| PGP3        |       |                                                                             |

| IDE 37X /   | 0     | DE 37X CHIP SELECT. OR ACTS AS PROGRAM MABLE OUTPUT PIN 2.                  |

| PGP2        |       |                                                                             |

| DEHDEN      | 0     | ENABLE DE CYCLE.                                                            |

| A 20M       | 0     | MASK PROCESSOR ADDRESS 20: ACTIVE W HEN GA20 IS LOW OR LO PORT              |

|             |       | 92H BIT 1 IS HIGH.                                                          |

| EXSM 12/LB2 | I     | EXTERNAL SMINPUT 2 OR ACTS AS LOW BATTERY 2 INPUT OR KEY                    |

| KBCLKI      |       | BOARD CLOCK INPUT.                                                          |

| FERR#       | I     | W HEN LOW INDICATES THAT A FLOATING POINT ERROR HAS OCCURRED.               |

| IGNNE#      | 0     | GNNE IS ASSERTED LOW TO INSTRUCT THE CPU TO IGNORE A NUMERIC                |

|             |       | ERROR AND CONTINUE EXECUTING NON-CONTROL FLOATING POINT                     |

|             |       | NSTRUCTIONS.                                                                |

| TEST        | I     | THIS PIN USED FOR TESTING ONLY FOR NORMAL OPERATION IT SHOULD               |

|             |       | BE PULLED HIGH.                                                             |

| VCC5        |       | +5V VOLT POW ER SUPPLY.                                                     |

| VCC 3       |       | 3.3-VOLT POW ER SUPPLY.                                                     |

## **5. PIN DESCRIPTIONS OF MAJOR COMPONENTS**

#### 5.5 C&T F65548 VGA CONTROLLER

| SYMBOL  | TY PE | DESCRIPTION                                          |

|---------|-------|------------------------------------------------------|

| RESET#  | I     | RESET FOR VL-BUS INTERFACES CONNECT TO RESET#.FOR    |

|         |       | DIRECT CPU LOCAL BUS INTERFACES , CONNECT TO THE     |

|         |       | SYSTEM RESET GENERATED BY THE MOTHERBOARD SYS-       |

|         |       | TEM LOGIC FOR ALL PERIPHERALS.                       |

| ADS#    | I     | ADDRESS STROBE. IN VL-BUS AND CPU LOCAL BUS INTER-   |

|         |       | FACES INDICATES VALID ADDRESS AND CONTROL SINGAL     |

|         |       | INFORMATION IS PRESENT.                              |

| M/10#   | I     | MEMORY IO. IN VL-BUS AND APU LOCALBUS INTERFACES     |

|         |       | NDICATES MEMORY OR LO CYCLE :1 = MEMORY ,0=LO        |

| W/R#    | I     | WRIFE / READ. THIS CONTROL SINGAL INDICATES A WRIFE  |

|         |       | (HIGH)OR READ (LOW )OPERATION. IT IS SAM PLED ON THE |

|         |       | RISING EDGE OF THE (INTERNAL)1x CPU CLOCK W HEN ADS# |

|         |       | IS ACTIVE.                                           |

| RDYRTN# | I     | READY RETURN HANDSHAKING SINGAL IN VL-BUS INTER-     |

| CRESET  | I     | FACES INDICATING SYNCHRONIZATION OF RDF# BY THE      |

|         |       | LOCAL BUS MASTER CONTROL TID THE PROCESSOR JPON      |

|         |       | RECEPT OF THIS LCLK-SYNCHRONOUS SIGNAL THE CHP       |

|         |       | W ILL STOP DRIVING THE BUS (IF A READ CYCLEWAS       |

|         |       | ACTIVE ) AND TERM INATE THE CURRENT CYCLE.           |

| LRDY#   | 0     | LOCAL READY . DRIVEN LOW DURING VL-BUS AND CPU       |

|         |       | LOCAL BUS CYCLES TO INDICATE THE CURRENT CYCLE       |

|         |       | SHOULD BE COMPLETED . THIS SIGNAL IS DRIVEN HIGH AT  |

|         |       | THE END OF THE CYCLE. THEN TRISTATED.                |

| LDEV#   | 0     | LOCAL DEVICE . IN VL-BUS AND CPU LOCAL BUS INTER-    |

|         |       | FACES, THIS PIN INDICATES THAT THE CHIP OW NS THE    |

|         |       | CURRENT CYCLE BASE ON THE MEMORY OR IO ADDRESS       |

|         |       | W HICH HAS BEED BROADCAST.                           |

| LCLK    | I     | LOCAL CLOCK . IN VL-BUS THIS PIN IS CONNECTED TO THE |

|         |       | CPU 1x CLOCK. IN CPU LOCAL BUS INTERFACES IT IS      |

|         |       | CONNECTED TO THE CPU 1x OR 2 x CLOCK JF THE INPUT IS |

|         |       | A $2x$ CLOCK, THE PROCESSORRESET SIGNAL MUST BE      |

|         |       | CONNECTED TO CRESET (PIN23) FOR SYNCHRON ZATION      |

|         |       | OF THE CLOCK PHASE.                                  |

| SYMBOL  | TY PE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BE0#    | I     | BYTE ENABLE 0.NDICATES DATA TRANSFER ON D7D0 FOR<br>THE CURRENT CYCLE.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| BE1#    | I     | BYTE ENABLE 1. NDICATES DATA TRANSFER ON D15D8<br>FOR THE CURRENT CYCLE.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| BE2#    | I     | BYTE ENABLE 2. INDICATES DATA TRANSFER ON D23D16<br>FOR THE CURRENT CYCLE.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| BE3#    | I     | BYTE ENABLE 3. BE3# INDICATES THAT DATA IS TO BE<br>TRANSFERRED OVER THE DATA BUS ON D31:24 DURING<br>THE CURRENT ACCESS.                                                                                                                                                                                                                                                                                                                                                                               |

| A(2:23) | I     | SYSTEM ADDRES BUS. IN VL-BUS, AND DIRECT CPU<br>INTERFACES, THE ADDRESS PINS ARE CONNECT DIRECTLY                                                                                                                                                                                                                                                                                                                                                                                                       |

| A24     | ΙØ    | TO THE BUS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| A25     | ΙQ    | ADDRESS INPUTS THROUGH A23 ARE ALW AYS AVA LABLE<br>A24-27 M AY BE OPTIONALLY USED FOR OTHER FUNCTION :                                                                                                                                                                                                                                                                                                                                                                                                 |

| A 26    | ΙØ    | <b>N</b> INTERNAL CLOCK SYNTHESIZER TEST MODE (TS# =0 AT                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| A 26    | TO    | RESET)A24 BECOM ES VCLK OUT AND A25 BECOM ES MCLK<br>OUT<br>A26 AND A27 MAY BE ALTRNATELY BE USE AS GENERAL<br>PURPOSE LO PINS OR ACTIVITY INDICATOR AND ENABLE<br>BACKLIGHT RESPECTIVELY (SEE PANEL INTERFACE PIN<br>DESCRIPTIONS AND XR5C AND XR72 FOR MORE DETAILS )<br>IF A26 AND A27 ARE USED AS GPD PINS, THEY MAY BE<br>PROGRAMMED AS 2-PIN CRT MONIFOR DDC INTERFACE.<br>EITHER A26 OR A27 MAY ALSO BE USED TO OUTPUT<br>COM POSITE SYNC. FOR SUPPORT OF AN EXTERNAL NTSC /<br>PAL ENCODER CHIP |

| D(0:31) | ΤΟ    | SYSTEM DATA BUS<br>N 32-BIT CPU LOCAL BUS DESIGNS THESE DATA LNES<br>CONNECT D RECTLY TO THE PROCESSOR DATA LNES.ON<br>THE VL-BUS THEY CINNECT TO THE CORRESPONDING<br>BUFFERED OR UNBUFFERED DATA SIGNAL.<br>THESE PINS ARE TRISTATED DURING STANDBY MODE                                                                                                                                                                                                                                              |

## **5. PIN DESCRIPTIONS OF MAJOR COMPONENTS**

#### 5.5 C&T F65548 VGA CONTROLLER

| SYMBOL     | TY PE | DESCRIPTION                                                     |

|------------|-------|-----------------------------------------------------------------|

| RESET#     | I     | RESET. THIS INPUT IS USED TO BRING SIGNALS AND                  |

|            |       | IN THE CHIP TO A CONSISTENT STATE.ALL OUTPUT FROM               |

|            |       | THE CHIPARE TRISTATED OR DRIVEN TO AN INACTIVE                  |

|            |       | STATE                                                           |

| CLK        | I     | BUS CLOCK .THIS INPUT PROVIDES THE TIM ING REFERENCE            |

|            |       | FOR ALL BUS TRANSACTION.                                        |

| PAR        | ΙЮ    | PARIRY .THIS SIGNAL IS USED TO MAINTAIN EVEN PARITY             |

|            |       | ACROSS ADO-31 AND C/BEO-3#.PAR IS STABLE AND VALID              |

|            |       | ONE CLOCK AFTER THE ADDRESS PHASE.                              |

| FRAM E#    | I     | CYCLE FRAME . DR VEN BY THE CURRENT MASTER TO                   |

|            |       | NDICAYE THE BEGINAND DURATION OF AN ACCESS.                     |

| IRDY#      | I     | NITATOR READY. NDICATE THE TARGET ABLITY TO                     |

|            |       | COM PLETE THE CURRENT DATA PHASE OF THE TRANS-                  |

|            |       | ACTON .                                                         |

| TRDY#      | S/TS  | TARGET READY. INDICATES THE TARGETS ABILITY TO                  |

|            |       | COMPLETE THE CURRENT DATA PHASE OF THE TRAN-                    |

|            |       | ACTION.                                                         |

| STOP#      | S/ST  | STOP. INDICATES THE CURRENT TARGET IS REQUESTING                |

|            |       | THE MASTER TO STOP THE CURRENT TRANSACTION                      |

| DEVSEL#    | S/ST  | DEVICE SELECT. INDICATES THE CURRENT TARGET HAS                 |

|            |       | DECODES ITS ADDRESS AS THE TARGET OF THE CURRENT                |

|            |       | ACCESS.                                                         |

| PESS#      | S/TS  | PARITY ERROR. THIS SIGNAL IS FOR THE REPORTING OF               |

|            |       | DATA PARITY ERRORS (EXCEPT FOR SPECIAL CYCLE                    |

|            |       | W HERE SERR# IS USED ).                                         |

| SERR#      | 0     | SYSTEM ERROR.USED TO REPORT SYSTEM ERROR WHERE                  |

|            |       | THE RESULT W ILL BE CATASTROPH $\mathbf \Gamma$ (ADDRESS PARITY |

|            |       | ERROR, DATA PARITY ERROR FOR SPECIAL CYCLE COM -                |

|            |       | MAND, ETC.)                                                     |

| ROMA(0:17) | 0     | BIDS ROM ADDRESS OUTPUT. SEE MAD8-15 (PIN170-177)               |

|            |       | FOR BIDS ROM DATA INPUT                                         |

| ROM OE#    | 0     | BIDS ROM OUTPUT ENABLE.                                         |

| AD(00:31)  | ΙØ    | PCIADDRESS /DATA BUS                                            |

| SYMBOL  | TY PE | DESCRIPTION                                        |

|---------|-------|----------------------------------------------------|

| C/BE0#  | I     | BUS COMMAND /BYTE ENABLES. DUR ING THE ADDRESS     |

|         |       | PHASE OF A BUS TRANSACTION , THESE PINS DEFINE THE |

|         |       | BUS COM M AND .(SEE LIST BELOW )                   |

| DSEL    | I     | NITALZATION DEVICE SELECT. USED AS A CHIP SELECT   |

|         |       | DURING CONFIGURATION READ AND WRITE TRANS-         |

|         |       | ACTION.                                            |

| AA0     | I/O   | ADDRESS BUS FOR DRAM S A AND B                     |

| AA1     |       |                                                    |

| A22     |       | PLEASE SEE THE CONFIGURATION TABLE IN THE EXTENDED |

| AA3     |       | REGISTER DESCRIPTION SECTION FOR COMPLETE DETAILS  |

| AA4     |       | ON THE CONFIGURATION OPTION FOR CFG0-8(XR01 AND    |

| AA5     |       | XR6C).                                             |

| ААб     |       |                                                    |

| AA7     |       |                                                    |

| AA8     |       |                                                    |

| CA(0:7) | 0     | ADDRESS BUS FOR DRAM C                             |

| CA8     |       | CA8MAY BECONFIGURED AS VAFC BLANK#OUT              |

| RASA#   | 0     | RAS FOR DRAM A                                     |

| RASB#   |       | RAS FOR DRAM B                                     |

| RASC#   |       | RAS FOR DRAM C OR COLOR KEY INPUT FROM EXTERNAL    |

|         |       | PC VIDEO SOURCE .                                  |

| CASAL#  | 0     | CAS FOR THE DRAM A LOW ER BYTE                     |

| CASAH#  |       | CAS FOR THE DRAM A UPPER BYTE                      |

| CASBL#  |       | CAS FOR THE DRAM B LOW ER BYTE                     |

| CASBH#  |       | CAS FOR THE DRAM B UPPER BYTE                      |

| CASCL#  | I/O   | DRAM C LOW BYTE VIDEO IN RED-6 OR VAFC VP14        |

| CASCH#  |       | DRAM C HIGH BYTE .VIDEO IN RED-7 OR VAFC VP15      |

| W EA#   | 0     | W RITE ENABLE FOR DRAM A                           |

| WEB#    |       | W RITE ENABLE FOR DRAM B                           |

| WEC#    |       | W RITE ENABLE FOR DRAM C OR VIDEO IN PORT PCLK OUT |

| OEAB#   | 0     | OUTPUT ENABLE FOR DRAM S A AND B                   |

| OEC#    |       | OUTPUT ENABLE FOR DRAMSC                           |

|         |       | OR VAFC "VIDEO INPUT CLOCK " IF DRAM C NOT USED    |

## **5. PIN DESCRIPTIONS OF MAJOR COMPONENTS**

#### 5.5 C&T F65548 VGA CONTROLLER

| SYMBOL    | TYPE | DESCRIPTION                                         |

|-----------|------|-----------------------------------------------------|

| MAD(0:15) | ΙÓ   | MEMORY DATA BUS FOR DRAM A (LOWER 512K OF           |

|           |      | DISPLAY MEMORY)                                     |